# Final Program

# AUMIL & Electronic Design, Security, IoT, Itonomous Vehicles, Quantum Computi

2025 26<sup>th</sup> International Symposium on

# QUALITY ELECTRONIC DESIGN

April 23-25, 2025

Seven Hills Conference Center

San Francisco State University

San Francisco, CA US

International Society for Quality Electronic Design Copyright© ISQED. All rights reserved. www.ISQED.com

# **Corporate Sponsors**

# **Technical Sponsors**

ISQED'25 is produced and sponsored by the International Society for Quality Electronic Design Copyright © 2025 All rights reserved

# **WELCOME TO ISQED'25**

It is with great pleasure that we welcome you to the 26th International Symposium on Quality Electronic Design (ISQED 2025). Building on last year's celebration of 25 years of innovation and leadership, this year's symposium continues our commitment to advancing the principles of Quality Electronic Design (QED) in an ever-evolving technological landscape.

In the spirit of accessibility and engagement, ISQED 2025 continues with a hybrid conference format—offering the richness of in-person interactions at the Seven Hills Conference Center at San Francisco State University, while also providing virtual access to participants worldwide. This blended approach allows us to connect a truly global community of innovators, researchers, and industry leaders.

ISQED has long stood at the forefront of driving progress in semiconductor design and electronic systems. This year's program builds on that legacy, presenting a dynamic agenda that includes keynote speeches, expert panels, hands-on tutorials, and more than 100 rigorously reviewed technical papers—all reflecting our unwavering focus on quality and innovation. This year's highlights include:

#### **Keynote Speakers**

Dr. Haoxing (Mark) Ren, Nvidia *Al for Chip Design*

Prof. Nael Abu-Ghazaleh, University of California, Riverside

Security and Privacy for Extended Reality Systems: Attacks and Threat Models

#### **Embedded Tutorials**

Dr. Zuguo (Joe) Wu, Intel

Scalable and Reliable On-Package I/O: UCle Innovations and Best Practices

Dr. Juthika Basak, AMD

Silicon Photonics for High Performance Computing

#### **Panel Discussion**

Cryogenic Electronics: Powering the Next Frontier in AI and Computing

We are proud to once again receive technical sponsorship from two premier IEEE societies—the Electron Devices Society and the Circuits and Systems Society—as well as the continued collaboration with ACM/SigDA. As always, ISQED proceedings will be published in the IEEE Xplore digital library and indexed in Scopus, ensuring that the knowledge shared here reaches a global scholarly audience.

Our 2025 program highlights transformative areas such as Artificial Intelligence and Machine Learning, Autonomous Systems, IoT, Cybersecurity, and Quantum Computing. Attendees can expect deep insights and forward-looking discussions across four parallel tracks, showcasing work at the intersection of theory and real-world application in circuits, systems, verification, and design automation.

This year's conference runs from April 23–25, Pacific Daylight Time (PDT), and every session—from plenaries to tutorials—will be accessible both on-site and online, reinforcing our dedication to inclusivity and knowledge-sharing across borders.

We extend our sincere thanks to our sponsors, Innovotek and Silicon Valley Polytechnic Institute, whose generous support continues to empower our mission and expand the impact of ISQED.

Welcome to ISQED 2025—where innovation, collaboration, and excellence come together to shape the future of quality electronic design.

General Chair Cindy Yi Virginia Tech

**Panels Chair**

Ahmedullah Aziz

The University of Tennessee, Knoxville

ISQED Founder & Chair Ali A. Iranmanesh Silicon Valley Polytechnic Institute **Technical Program Chair** *Hossein Sayadi*California State University, Long Beach

**Tutorials Chair Zhen Zhou** Intel Corporation **Technical Program Co- Chair Deliang Fan**Arizona State University

Publication Chair Paul Wesling Hewlett Packard (retired)

# **ISQED'25 Best Papers**

#### 1C.1

# AutoFlows: Inferring Message Flows From System Communication Traces

Bardia Nadimi, Hao Zheng

Department of Computer Science and Engineering

University of South Florida

#### 2A.2

## VRank: Enhancing Verilog Code Generation from Large Language Models via Self-Consistencyand Simulation Schemes

Zhuorui Zhao<sup>1</sup>, Ruidi Qiu<sup>1</sup>, Ing-Chao Lin<sup>2</sup>, Grace Li Zhang<sup>3</sup>, Bing Li<sup>4</sup>, Ulf Schlichtmann<sup>1</sup>

<sup>1</sup>Chair of Electronic Design Automation, Technical University of Munich (TUM), Munich, Germany

<sup>2</sup>Computer Architecture and IC Design, National Cheng Kung University

<sup>3</sup>Hardware for Artificial Intelligence Group, Technical University of Darmstadt

<sup>4</sup>Research Group of Digital Integrated Systems, University of Siegen

Authors of best papers are acknowledged during the morning plenary session on Wednesday April 23. ISQED'25 best papers are sponsored by **Silicon Valley Polytechnic Institute**.

# **ISQED'25 Organizing Committee**

**Program Chair** Hossein Sayadi California State University,

Long Beach

**Panel Chair** Ahmedullah Aziz

The University of Tennessee, Knoxville

**Plenary Chair** Ali A. Iranmanesh Silicon Valley Polytechnic Institute **Program Co-Chair** Deliana Fan Arizona State University

**General Chair** Cindy Yi Virginia Tech

**Tutorials Chair** Zhen Zhou Intel Corporation

**Publication Chair Paul Wesling** Hewlett Packard (Retired)

# TECHNICAL PROGRAM COMMITTEES

Cognitive Computing Hardware (CCH)

Caiwen Ding, University of Minnesota Twin Cities (Chair)

Zhen Zhou, Intel Corp (Co-Chair)

**Committee Members:**

Divya Akella Kamakshi - NVIDIA

Hongyu An - Michigan Technological University

Kang Jun Bai - Air Force Research Laboratory

Sathwika Bavikadi - Rochester Institute of Technology

Weidong Cao - The George Washington University

Gourav Datta - Amazon

Deliang Fan - Arizona State University

**Haowen Fang - Synopsys**

Darshan Gandhi - Sambanova Systems Inc

Shaoyi Huang - Stevens Institute of Technology

Doo Seok Jeong - Hanyang University

Hao Jiang - San Francisco State University

Mehdi Kamal - University of Southern California

Xiaolong Ma - Clemson University

**Gopal Raut - CDAC Bangalore**

Ao Ren - Chongging University

Ishan Thakkar - University of Kentucky

Dongkuan Xu - North Carolina State University

Cindy Yang Yi - Virginia Tech

Miao Yin - University of Texas at Arlington

Geng Yuan - University of Georgia

## **Design Test and Verification (DTV)**

Chidhambaranathan Rajamanikkam, Synopsys Inc.(Chair)

Sumit Jha, Florida International University (Co-Chair)

**Committee Members:**

George Alexiou - Univ. Of PATRAS

Michael Hsiao - Virginia Tech

Chrysovalantis Kavousianos - University of Ioannina

**Dimitris Nikolos - University of Patras**

**Sushant Sadangi - Intel Corporation**

Yiorgos Tsiatouhas - University of Ioannina

Miroslay Veley - Aries Design Automation

Arnaud Virazel - LIRMM

Heng Wu - Peking University zhichao Zhang - Intel

# **TECHNICAL PROGRAM COMMITTEES**

(continued)

#### Electronic Design Automation Tools and Methodologies (EDA)

Srinivas Katkoori, University of South Florida (Chair)

Srini Krishnamoorthy, Intel Corp. (Co-Chair)

**Committee Members:**

Pravin Chandran - Intel

Abishai Daniel - Micron

**Dhruva Ghai - ORIENTAL UNIVERSITY INDORE**

**Zhong Guan - UC Santa Barbara**

Xinfei Guo - Shanghai Jiao Tong University

Sandeep Hari - Uhnder Inc

Shih-Hsu Huang - Chung Yuan Christian University

Leslie Hwang - Arizona State University

Sheikh Ariful Islam - University of Texas Rio Grande Valley

**Anand Iyer - Synopsys**

Yu-Min Lee - National Yang Ming Chiao Tung University

Zhixing Li - Synopsys

Rung-Bin Lin - Yuan Ze University

**Bin Lin - Cadence Design Systems**

Zizhen Liu - Institute of Computing Technology Chinese Academy of Sciences

Ofelya Manukyan - Synopsys Inc.

Rajeev Murgai - Synopsys India Pvt. Ltd.

Murthy Palla - Synopsys Inc.

Chidhambaranathan Rajamanikkam - Synopsys Inc.

**Andre Reis - UFRGS**

**Emre Salman - Stony Brook University**

**Ioannis Savidis - Drexel University**

Jia Wang - Illinois Institute of Technology

Hua Xiang - IBM Research

Kexin Yang - Google

Richard Yarnell - University of Central Florida

Huan Yu - Apple

**Rui Zhang - Cadence Design Systems**

Lining Zhang - Peking University

#### System-level Design and Methodologies (SDM)

Bo Yuan, Rutgers University (Chair)

Jeff Zhang, Arizona State University (Co-Chair)

#### **Committee Members:**

Mohamad Hammam Alsafrialani - University of Miami

Kunvar Chokshi - Tesla Inc.

**Sourav Das - Intel Corporation**

Andrea Guerrieri - EPFL and HES-SO

Fabiano Hessel - PUCRS

Sahidul Islam - The University of Texas at San Antonio

Hana Kubatova - Czech Technical University in Prague

**Abdulrahman Mahmoud - Harvard University**

Carlos Moratelli - UFSC

Sergiu Mosanu - University of Virginia

Antonio Nunez - University of Las Palmas GC

Jan Schmidt - Czech Technical University in Prague

Jihee Seo - Synopsys

Vaibhav Verma - Qualcomm

Sai Qian Zhang - New York University

# **TECHNICAL PROGRAM COMMITTEES**

(continued)

#### Circuit Design, 3D Integration and Advanced Packaging (ICAP)

Abhronil Sengupta, The Pennsylvania State University (Chair)

Rouwaida Kanj, Synopsys/American University of Beirut(adjunct) (Co-Chair)

Harsh Patel, Rivos Inc. (Co-Chair)

**Committee Members:**

Ali Afzali-Kusha - University of Tehran

**Amit Agarwal - Intel Corporation**

Iraklis Anagnostopoulos - Southern Illinois University Carbondale

Kirti Bhanushali - Cadence Design Systems

Karan Bhatia - Texas Instruments, Inc.

Paulo Butzen - Universidade Federal do Rio Grande Sul

Yuanqing Cheng - Beihang University

Marshnil Dave - Lion Semiconductor

**Tobias Gemmeke - RWTH Aachen University**

Na Gong - University of South Alabama

Abhilash Goyal - IEEE Member

Ankur Guha Roy - Broadcom Inc.

Steven Hsu - Intel Corp.

Manjunath Kareppagoudr - Advanced Micro Devices inc

Dae Hyun Kim - Washington State University

**Rakesh Kumar - Ampere Computing**

Jin-Fu Li - National Central University

Rakeshkumar Mahto - California State University, Fullerton

Maruthi Mukkannaiah - iota Biosciences

Vojin Oklobdzija - University of California Davis

Krishna Pentakota - Skyworks Solutions, Texas A&M University

**Praveen Prabha - Marvell Semiconductor**

Suyash Ranjan - Qualcomm

Joseph Riad - Micron Technology

Thilo Sauter - Danube University Krems

**Ioannis Savidis - Drexel University**

Ali Shahi - GlobalFoundries

**Hechen Wang - Intel Labs**

Yanchao Wang - Broadcom

zhichao Zhang - Intel

Zhen Zhou - Intel Corp

Amir Zjajo - Innatera Nanosystems

Special Sessions (SS)

Hossein Sayadi, California State University, Long Beach (Co-Chair)

# **TECHNICAL PROGRAM COMMITTEES**

(continued)

#### **Hardware and System Security (HSS)**

Hassan Salmani, Howard University (Chair)

#### **Committee Members:**

Kanad Basu - University of Texas at Dallas

Alvaro Cintas Canto - Marymount University

Avani Dave - Intel Corp. Inc

Everton de Matos - Technology Innovation Institute

Caiwen Ding - University of Minnesota Twin Cities

Jaya Dofe - California State University

Subhajit Dutta Chowdhury - AMD

Tasnuva Farheen - Louisiana State University

Dominik Germek - Corporate Research Robert Bosch GmbH

Yinghua Hu - Synopsys

Chenglu Jin - CWI Amsterdam

**Kyle Juretus - Villanova University**

Mehran Mozaffari Kermani - University of South Florida

Debdeep Mukhopadhyay - Department of Computer Science and Engineering, Indian Institute of Technology Kharagpur

**Hammond Pearce - University of New South Wales**

Md Tauhidur Rahman - Florida International University

Biswajit Ray - Colorado State University

Francesco Regazzoni - University of Amsterdam and Università della Svizzera italiana

Amin Rezaei - California State University, Long Beach

Soheil Salehi - Department of Electrical and Computer Engineering, University of Arizona

fareena saqib - University of North Carolina at Charlotte

Zhijie Shi - University of Connecticut

**Benjamin Tan - University of Calgary**

Jiafeng Xie - Villanova University

Lian Zeng - Infineon Techologies

Jiliang Zhang - Hunan University

## **Emerging Device and Process Technologies and Applications (EDPT)**

Rasit Onur Topaloglu, Adeia (Chair)

Lan Wei, University of Waterloo (Co-Chair)

**Committee Members:**

Shaahin Angizi - New Jersey Institute of Technology

Ahmedullah Aziz - University of Tennessee, Knoxville

Arijit Banerjee - Advanced Micro Devices

**Sumeet Gupta - Purdue University**

Vita Pi-Ho Hu - National Taiwan University

**Huamin Li - University at Buffalo**

Chun-Yu Lin - National Yang Ming Chiao Tung University

Ankita Mohapatra - Associate Professor

Mehran Mozaffari Kermani - University of South Florida

Chenyun Pan - University of Texas at Arlington

**Kun Qian - GLOBALFOUNDRIES**

Uiwal Radhakrishna - Texas Instruments Inc.

Arman Roohi - University of Illinois Chicago

Sonal Shreya - Aarhus University

Yanan Sun - Department of Micro-Nano Electronics, Shanghai Jiao Tong University

Jinhui Wang - University of South Alabama

Zhaohao Wang - Beihang University

Mustafa Berke Yelten - Istanbul Technical University

## **GENERAL INFORMATION**

# GENERAL INFORMATION ISOED'25

April 23-25, 2025 Seven Hills Conference Center San Francisco State University

#### **AWARDS & RECOGNITIONS**

Wednesday April 23, 8:40 AM - 9:00 AM

Track A - Nob Hill Room

## **Best Paper Awards**

Recipients of the ISQED'25 Best Paper Awards will be recognized in this segment of the program. The best papers are shown in Page 2 of this document.

## Keynotes Keynote 1P.1

Wednesday, April 23, 9:00 AM - 9:35 AM

# Al for Chip Design: Unlocking New Frontiers in Automation and Scaling

Dr. Haoxing (Mark) Ren Nvidia

**Keynote 2P.1**

Thursday, April 24, 9:00 AM - 9:35 AM

# Security and Privacy for Extended Reality Systems: Attacks and threat models

Prof. Nael Abu-Ghazaleh UC Riverside

#### **Panel Discussion**

Wednesday, April 23, 3:15 PM - 4:45 PM

Track A - Nob Hill Room

# Cryogenic Electronics: Powering the Next Frontier in Al and Computing

As we push the limits of performance in computing, sensing, and quantum technologies, cryogenic electronics has emerged as a trailblazing frontier in modern engineering. This panel will dive into the rapidly evolving field of electronics designed to operate at ultra-low temperatures, where new physics and unprecedented efficiencies become possible. Experts from across the field will share insights on groundbreaking innovations that exploit the unique properties of superconductors, cryogenic memory, and quantum devices to unlock new levels of speed, energy efficiency, and precision. From enabling scalable quantum processors to advancing ultra-sensitive sensors for space and science, cryogenic electronics holds transformative potential across various industries. Join us for an inspiring discussion on the latest breakthroughs, key challenges, and the future directions of cryogenic technology. This is a rare opportunity to gain a deep understanding of the innovations that could redefine computing, data processing, and sensing in the age of extreme electronics.

#### **Panelists:**

Dr. Patricia Gonzalez - Lawrence Berkeley National Lab

Dr. James Tandon - cassia. Al

Dr. Hiu-Yung Wong - San Jose State University

#### **Modedrator & Chair:**

Dr. Ahmedullah Aziz - University of Tennessee Knoxville

# **GENERAL INFORMATION**

## **Embedded Tutorials**

#### <u>Chair & Moderators:</u> **Zhen Zhou** - Intel (Chair)

## Track A - Nob Hill Room Tutorial 1

Wednesday, April 23, 12:25 PM -1:25 PM

Scalable and Reliable On-Package I/O: UCle Innovations and Best Practices

Dr. Zuguo (Joe) Wu Intel

# **Tutorial 2**

Thursday April 24, 1:05 PM -2:05 PM

Optical Transceivers Enabling High Performance Hardware Infrastructure for AI applications

> **Dr. Juthika Basak** AMD

#### **TECHNICAL SESSIONS**

. . . . . . . . . . . . .

There are a total of 23 paper sessions held on Wednesday to Friday. Technical sessions are held in the format of three parallel tracks **A**, **B**, **C** located respectively in Nob Hill Room, Russian Hill Room, and Mt. Davidson room.

#### ON-SITE REGISTRATION

Tentative time schedule of on-site registration is as follows:

Wednesday, April 23, 8:00 AM - 2:00 PM Thursday, April 24, 8:00 AM - 12:00 PM

Registration desk location will be at the conference center lobby.

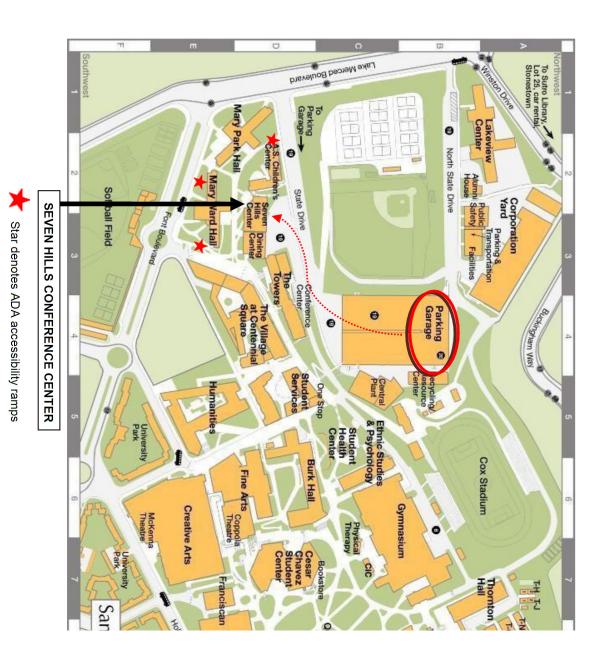

#### Seven Hills Conference Center

ISQED'25 conference will be held in Seven Hills Conference Center, located in San Francisco State University, 800 Font Blvd, San Francisco, CA 94132.

If you are using navigator the best address to use is: 796 state drive, San Francisco, CA 94132. (Note: make sure to use Google Maps app) At the end of State Drive is the Public Parking Lot ("Lot 20"). Parking is \$6.25 for less than 2 hours, and \$10 for 2+ hours. Pay stations on each floor accept \$1, \$5 and \$10 bills as well as credit/debit cards. Be advised, pay stations do not provide change. Please have exact amount. From the garage, Seven Hills' entrance can be accessed from State Drive by walking Southwest towards the A.S. Children's Center and taking the staircase beside it up one flight. Wheelchair access: go past the A.S. Children's Center and take a left onto the path. Follow to the entrance to the Seven Hills Conference Center.

# **UNIVERSITY MAP & CONFERENCE CENTER LOCATION+**

# **PROGRAM AT A GLANCE**

# **WEDNESDAY APRIL 23**

|  | 15:15pm-16:45pm                                                       |                                              | 15:10pm-15:15pm                                                         | 13:30pm-15:10pm                                                                                            | 3                                                         | 13:25pm-13:30pm | 12:25pm-13:25am                                                               |                      | 11:40am-12:25pm |                                                                            | 10:20am-11:40am                                             | 10:10am-10:20am | 9:35am-10:10am | 9;00am-9:35am                                                                                                  | 8:40am-9:00am                                           |                                             |

|--|-----------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------|-------------------------------------------------------------------------------|----------------------|-----------------|----------------------------------------------------------------------------|-------------------------------------------------------------|-----------------|----------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------|

|  | Cryogenic Electronics: Powering the Next Frontier in AI and Computing | Panel Discussion - (Track A - Nob Hill Room) | Break                                                                   | -                                                                                                          | Session 2A (Nob Hill Room) Session  Generative Al and its |                 | Scalable and Reliable On-Package I/O: UCIe  Presenter: Zuguo (Joe) Wu - Intel | )<br>Ige I/O: UCIe I |                 | ligh-                                                                      | Session 1A (Nob Hill Room)  Room)  Innovations in In-Memory |                 | Break          | Keynote: Al for Chip Design: Unlocking New Frontiers in Automation and Scaling Dr. Haoxing (Mark) Ren - Nvidia | Introduction, Committee Recognitions, Best Paper Awards | Plenary Session 1: (Track A- Nob Hill Room) |

|  |                                                                       | om)                                          |                                                                         | Security-aware Design Flow for Efficient Hardware Integeretaed Circuits Architectures for Approximate Comp | Session 2B (Russian Hill Session 2C Room) Room)           | Break           | Innovations and Best Practices                                                |                      | Lunch Break     | Security Primitives in Modern Design Verification and Speed Memory Testing | Session 1<br>Room)                                          | Break           |                |                                                                                                                |                                                         |                                             |

|  |                                                                       |                                              | Efficient Hardware<br>Architectures for Al and<br>Approximate Computing | C (Mt. Davidson                                                                                            |                                                           |                 |                                                                               |                      | mory Testing    | Session 1C (Mt. Davidson<br>Room)                                          |                                                             |                 |                |                                                                                                                |                                                         |                                             |

# **PROGRAM AT A GLANCE**

# **THURSDAY APRIL 24**

| 14:05pm-14:10pm<br>14:10pm-15:50pm                                             | 13:05pm-14:05pm                                                                                                                                                                  | 12:25pm-13:05 | 10:45am-12:25pm                                                                                  | 10:35am-10:45am | 9:40am-10:35am                                                                       | 9:35am-9:40am | 8:45am-9:00am<br>9:00am-9:35am                                                                                                                                       |                                              |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Session 4A (Nob Hill Room) VLSI Physical Design Methodologies                  | Embedded Tutorial 2 (Track A - Nob Hill Room) Optical Transceivers Enabling High Performance Presenter: Juthika Basak - AMD                                                      |               | Session 3A (Nob Hill Room) Simulation and Analysis in VLSI Design                                |                 | Session PW1 (Nob Hill Room,<br>Track A)<br>Short Presentation & WIP<br>Session 1     |               | Keynote: Security and Privacy for Extended Reality Systems: Attace Prof. Nael Abu-Ghazaleh - University of California, Riverside                                     | Plenary Session 2: (Track A - Nob Hill Room) |

| Session 4B (Russian Hill<br>Room)<br>Security Evaluation in Complex<br>Designs | Embedded Tutorial 2 (Track A - Nob Hill Room)  Optical Transceivers Enabling High Performance Hardware Infrastructure for Al applications  Presenter: Juthika Basak - AMD  Break | Lunch Break   | Session 3B (Russian Hill<br>Room)<br>Recent Trends in Cognitive<br>Computing Hardware            | Break           | Session PW2 (Russian Hill<br>Room, Track B)<br>Short Presentation & WIP<br>Session 2 | Break         | Welcome Keynote: Keynote: Security and Privacy for Extended Reality Systems: Attacks and threat models Prof. Nael Abu-Ghazaleh - University of California, Riverside | ob Hill Room)                                |

| Session 4C (Mt. Davidson<br>Room)<br>Generative AI on Edge                     | cture for Al applications                                                                                                                                                        |               | Session 3C (Mt. Davidson<br>Room)<br>Neuromorphic Computing for<br>Next-gen Machine Intelligence |                 | Session PW3 (Mt. Davidson<br>Room, Track C)<br>Short Presentation & WIP<br>Session 3 |               | threat models                                                                                                                                                        |                                              |

# **FRIDAY APRIL 25**

| 12:55pm-14:55pm                                                | 12:25pm-12:55                              | 10:45am–12:05pm                                                           | 10:40am-10:45am                | 9:00am-10:40am                                                                                        |  |

|----------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------|--|

|                                                                |                                            | Advances in Quantum Computing: Security, Optimization, and Al Integration | Session 6A (Nob Hill Room)     | Session 5A (Nob Hill Room) Memristive and Charge-Trap Devices for Next-Gen Computing                  |  |

| Optimizing Memory, Power, and Computation for Next-Gen Systems | Lunch Break Session 7B (Russian Hill Room) | Advanced Signal Processing and Al Acceleration                            | Session 6B (Russian Hill Room) | Session 5B (Russian Hill<br>Room)<br>Al-Driven Embedded<br>Computing and Power-Aware<br>System Design |  |

| Hardware Techniques in Quantum Computing Security              | Session 7C (Mt. Davidson                   | Intelligent and Secure Computing for Next-Gen Systems                     | Session 6C (Mt. Davidson Room) | Session 5C (Mt. Davidson Room)  Design Innovation and Accelaration in the Nanometer Era               |  |

# **ISQED Keynote 1P.1**

# Wednesday April 23

9:00 AM - 9:35 AM Room: Nob Hill

# Al for Chip Design: Unlocking New Frontiers in Automation and Scaling

Dr. Haoxing (Mark) Ren

Director of Design Automation Research - Nvidia

The history of EDA is fundamentally a story of two parallel trends: increasing automation of manual design tasks and the scaling of these automation techniques to handle ever-larger design complexities. Today, with generative AI and accelerated computing, we are entering a new phase that promises to dramatically advance both fronts. In this talk, I will explore how these technologies can drive the next wave of innovation in EDA. While current commercial offerings in AI for chip design have shown promising progress, the path ahead holds even greater opportunities for innovation and impact. I will present examples from physical and logic design to illustrate how generative AI and GPU-accelerated computing can further enhance automation and enable greater scaling. Specifically, I will cover our recent work on LLM-based gate sizing, synthetic data generation for RTL design, model merging for domain-adapted LLMs, and agent-based RTL coding and debugging. Together, these developments underscore the transformative potential of generative AI and accelerated computing to automate more tasks and scale chip design workflows like never before.

#### About Haoxing (Mark) Ren

Haoxing (Mark) Ren is the Director of Design Automation Research at NVIDIA, focusing on leveraging machine learning and GPU-accelerated tools to enhance chip design quality and productivity. He has over 25 years of industrial EDA research and development experience at IBM and NVIDIA. He holds over thirty patents and has co-authored over 100 papers and books, including a book on ML for EDA and several book chapters in EDA. He received several prestigious awards for his work, including the IBM Corporate Award and best paper awards at ISPD, DAC, TCAD, MLCAD and LAD. He serves in the organization and steering committees of international conferences such as ICCAD and ISPD and as the conference chair at ICLAD. He holds Bachelor's and Master's degrees from Shanghai Jiao Tong University and Rensselaer Polytechnic Institute, respectively, and earned his PhD from the University of Texas at Austin. He is a Fellow of the IEEE.

# **ISQED Keynote 2P.1**

Thursday April 24 9:00 AM - 9:35 AM Room: Nob Hill

# Security and Privacy for Extended Reality Systems: Attacks and threat models

Dr. Nael Abu-Ghazaleh

Professor in the CSE department, UC Riverside

AR/VR devices promise a new era of immersive computing, where our everyday experience is augmented with helpful information (Augmented Reality), or where we are immersed in fully virtual worlds (Virtual Reality). These systems fuse the physical world, and the virtual world, through computing resources to provide these immersive experiences rendered on the user's headset. As a result, it allows new opportunities for attackers to compromise the security and privacy of users, that are not well understood. Towards understanding the security and privacy challenges in these systems, this talk presents a number of recent attacks we developed on AR/VR systems. One threat model exploits the shared computing resources used by multiple applications on a headset to extract information through side channels; we show attacks that spy on user activity or compromise privacy. Another threat model exploits the shared state among multiple users in a multi-user application, allowing malicious users to inject compromised information or to recover information they are not allowed to access. Other threat models include those that interfere with applications and cause the virtual model to become out of sync with the physical world, causing user motion sickness or bypassing safety guardrails. I will conclude with discussion potential defenses and ways to build more security AR/VR experiences.

#### **About Nael Abu-Ghazaleh**

Nael Abu-Ghazaleh is a Professor in the Computer Science and Engineering as well as the Electrical and Computer Engineering Departments at the University of California, Riverside. His research is in architecture and system security, high-performance computing, and systems and security for Machine Learning. He has published over 250 papers in these areas, several of which have been recognized with best paper awards or nominations. His offensive security research has resulted in the discovery of several new attacks on CPUs and GPUs that have been disclosed to companies including Intel, AMD, ARM, Apple, Microsoft, Google, and Nvidia, and resulted in patches and modifications to products, and coverage from technical news outlets. He is a member of the Micro Hall of Fame, an ACM distinguished member, and an IEEE distinguished speaker.

# **Panel Discussion**

Wednesday April 23 3:25 PM-4:55 PM Room: Nob Hill

# Cryogenic Electronics: Powering the Next Frontier in Al and Computing

#### **Panelists:**

Dr. Patricia Gonzalez - Lawrence Berkeley National Lab

Dr. James Tandon - cassia. Al

Dr. Hiu-Yung Wong - San Jose State University

## **Modedrator/Chair:**

**Dr. Ahmedullah Aziz -** University of Tennessee Knoxville

## **Summary**:

As we push the limits of performance in computing, sensing, and quantum technologies, cryogenic electronics has emerged as a trailblazing frontier in modern engineering. This panel will dive into the rapidly evolving field of electronics designed to operate at ultra-low temperatures, where new physics and unprecedented efficiencies become possible. Experts from across the field will share insights on groundbreaking innovations that exploit the unique properties of superconductors, cryogenic memory, and quantum devices to unlock new levels of speed, energy efficiency, and precision. From enabling scalable quantum processors to advancing ultra-sensitive sensors for space and science, cryogenic electronics holds transformative potential across various industries. Join us for an inspiring discussion on the latest breakthroughs, key challenges, and the future directions of cryogenic technology. This is a rare opportunity to gain a deep understanding of the innovations that could redefine computing, data processing, and sensing in the age of extreme electronics.

# **Embedded Tutorial 1**

Wednesday April 23

12:25 AM - 1:25 PM

Nob Hill Room

# Scalable and Reliable On-Package I/O: UCIe Innovations and Best Practices

Dr. Zuguo (Joe) Wu Intel

## **Summary:**

The transition from traditional System On Chip (SOC) designs to chiplet-based architectures marks a significant evolution in semiconductor technology. This presentation will explore the Universal Chiplet Interconnect Express (UCle), an open standard that ensures seamless chiplet interoperability within a package. We will delve into the critical innovations of UCle, highlighting its electrical characteristics, 2D/2.5D/3D packaging, and energy-efficient design that collectively achieve a tenfold reduction in power consumption compared to conventional off-package I/O. A key focus will be on the reliability of densely packed UCle links, examining the considerations of consistent and error-free data transmission, even at elevated data rates.

#### About Zuguo (Joe) Wu

Zuoguo Wu is a Senior Principal Engineer at Intel, where he manages an I/O circuits and architecture team working on the latest interfaces. He currently serves as the UCle Consortium Electrical Working Group Co-Chair. He is a principal author of the UCle spec and defined its PHY architecture and circuit and link analysis. He is also a key contributor to every generation of the PCle spec since 3.0. He holds 147 patents worldwide and has published over 50 external and Intel-internal papers. He earned a PhD in electrical engineering from Texas A&M University.

# **Embedded Tutorial 2**

Thursday April 24 1:05 PM - 2:05 PM Nob Hill Room

# Optical Transceivers Enabling High Performance Hardware Infrastructure for Al applications

**Dr. Juthika Basak** *AMD*

# Summary:

In recent years, Large Language Models (LLMs) have played a significant role in advancing Generative Artificial Intelligence (Gen AI). The amount of compute needed (in petaFLOPs) to support such LLMs has grown at an exorbitant rate of approximately 750x every 2 years. However, interconnect, DRAM, and hardware bandwidth have not progressed at the same rate, prompting the semiconductor industry to explore disruptive technologies. Optical interconnects, which have become widespread in long haul and metro haul network applications, offer a promising solution. The need for cost-efficient solutions has also hastened adoption of silicon photonics transceivers, in turn driving design and manufacturing innovations in this domain. Silicon Photonics Integrated Circuits (PICs) also lends itself well to the advanced packaging schemes, such as hybrid bonding to the associated analog circuits, viz. drivers and Transimpedance Amplifiers (TIAs). This results in signal integrity interconnects in compact form-factors. This tutorial delves into the fundamentals of optical transceivers, exploring the challenges and opportunities associated with incorporating optics into AI-centric hardware infrastructure.

#### **About Juthika Basak**

Juthika Basak is a Fellow at Advanced Micro Devices (AMD) working on cutting edge of Photonics Technologies for improving interconnect bandwidth and increasing compute capacities. Prior to AMD, Juthika worked at Nokia, architecting and leading its new generation of CSTAR (Coherent Silicon Transmitter and Receiver) Trademark product line. She also managed the Advanced Packaging technology development team, delivering multiple generations of coherent products for long haul networks. Juthika also worked at Finisar (acquired by II-VI Corporation and further renamed as Coherent), designing pluggable transceivers for long haul interconnect applications. Leading up to her work on transceiver design, she spent several years at Intel Corporation and Infinera Corporation, working on silicon and III-V photonics technologies, respectively. She completed her B. Tech. in Engineering Physics from the Indian Institute of Technology, Bombay and her M.S. and Ph.D. in Electrical Engineering from University of California, Los Angeles.

# ISQED 2025: Program

#### SESSION 1A

## Wednesday April 23

## Innovations in In-Memory Computing for AI and High-Performance Hardware

Chair: Ahmedullah Aziz, The University of Tennessee, Knoxville

10:15AM

1A.1

# **In-Memory Template Matching with Approximated PCC Computation Leveraging Memristive System**

Sree Nirmillo Biswash Tushar<sup>1</sup>, Sk Hasibul Alam<sup>1</sup>, Graham Buchanan<sup>1</sup>, Rocco Febbo<sup>1</sup>, Hritom Das<sup>2</sup>, Garrett Rose<sup>1</sup>

<sup>1</sup>University of Tennessee, Knoxville, <sup>2</sup>Oklahoma State University

10:35AM

1A.2

# An Error-resilient Compute-in-memory 3D FPCA Architecture for High-performance Floating-point Operations

Hasita Veluri and Dilip Vasudevan Lawrence Berkeley National Laboratory

10:55AM

1A.3

# **HIDE:** A Hyperdimensional In-DRAM Encoder for Fast and Energy-Efficient Classification

Ahmed Mamdouh and Dayane Reis University of South Florida

## **SESSION 1B**

## Wednesday April 23

## **Security Primitives in Modern Designs**

Chair: Hossein Sayadi, California State University, Long Beach

10:15AM

1B.1

# **XORed Carry Chain Ring Oscillator Factored True Random Number Generator**

Kanish R<sup>1</sup> and Madhav Rao<sup>2</sup>

<sup>1</sup>International Institute of Information Technology Bangalore, <sup>2</sup>International Institute of Information Technology-Bangalore

10:35AM

1B.2

# Non-Homogeneous Composite Karatsuba Multipliers Factored Hardware-Efficient ECDSA Generation and Verification Accelerator Units

Pruthvi Parate<sup>1</sup>, Alwin Shaju<sup>1</sup>, Sanampudi Gopala Krishna Reddy<sup>1</sup>, Vasanthi D R<sup>1</sup>, Madhav Rao<sup>2</sup>

<sup>1</sup>International Institute of Information Technology Bangalore, <sup>2</sup>International Institute of Information Technology-Bangalore

10:55AM

1B.3

# Device Boot-up Security Restoration with Post-Quantum Split-key KEM

Joonas Ahola, Jan-Erik Ekberg, Sampo Sovio Huawei Technologies Oy

11:15AM

1B.4

# Quantum Data Breach: Reusing Training Dataset by Untrusted Quantum Clouds

Suryansh Upadhyay<sup>1</sup> and Swaroop Ghosh<sup>2</sup>

<sup>1</sup>Penn State University, <sup>2</sup>Pennsylvania State University

11:35AM

1B.5

RollGuard: Defending RPC Manipulation Attacks in Optimistic Rollups with Graph  $\operatorname{ML}$

Alvi Ataur Khalil and Mohammad Ashiqur Rahman Florida International University

## **SESSION 1C**

## Wednesday April 23

## **Design Verification and High-Speed Memory Testing**

Chair: Chidhambaranathan Rajamanikkam, Synopsys Inc.

10:15AM

1C.1

## **AutoFlows: Inferring Message Flows From System Communication Traces**

Bardia Nadimi and Hao Zheng University of South Florida

10:35AM

1C.2

# Automated Verilog Assertion Generation Using Fine-Tuned LLMs with Subtask-Specific Iterative Prompting

Mohammad Shahidzadeh<sup>1</sup>, Behnam Ghavami<sup>2</sup>, Steve Wilton<sup>3</sup>, Lesley Shannon<sup>1</sup>

<sup>1</sup>Simon Fraser University, <sup>2</sup>Advanced Micro Devices (AMD), <sup>3</sup>University of British Columbia

10:55AM

1C.3

# Leveraging DDR5 RCDs for High-Speed DDR5 Protocol Analysis: A Novel Approach to RDIMM Testing

Xinran Li

Professional

11:15AM

1C.4

# Formal Verification of a Custom Compiler for a Fully Homomorphic Encryption Accelerator

Zhenkun Yang<sup>1</sup>, Suvadeep Banerjee<sup>2</sup>, Jeremy Casas<sup>1</sup>, Jin Yang<sup>1</sup> Intel Corporation, <sup>2</sup>Intel Labs, Intel

#### **SESSION 2A**

## Wednesday April 23

# Generative AI and its Application to Design Automation

Chair: Chidhambaranathan Rajamanikkam, Synopsys Inc.

1:40PM

2A.1

# **EDA-Debugger: An LLM-based Framework for Automated EDA Runtime Issue Resolution**

Junyan Li<sup>1</sup>, Sam-Zaak Wong<sup>2</sup>, Gwok-Waa Wan<sup>2</sup>, Xi Wang<sup>1</sup>, Yang Jun<sup>3</sup>

<sup>1</sup>Southeast University, <sup>2</sup>NCTIEDA, <sup>3</sup>

2:00PM

2A.2

# VRank: Enhancing Verilog Code Generation from Large Language Models via Self-Consistency

Zhuorui Zhao<sup>1</sup>, Ruidi Qiu<sup>1</sup>, Ing-Chao Lin<sup>2</sup>, Grace Li Zhang<sup>3</sup>, Bing Li<sup>4</sup>, Ulf Schlichtmann<sup>1</sup> <sup>1</sup>Technical University of Munich, <sup>2</sup>National Cheng Kung University, <sup>3</sup>TU Darmstadt, <sup>4</sup>University of Siegen

2:20PM

2A.3

# Paradigm-Based Automatic HDL Code Generation Using LLMs

Wenhao Sun<sup>1</sup>, Bing Li<sup>2</sup>, Grace Li Zhang<sup>3</sup>, Xunzhao Yin<sup>4</sup>, Cheng Zhuo<sup>4</sup>, Ulf Schlichtmann<sup>1</sup> Technical University of Munich, <sup>2</sup>University of Siegen, <sup>3</sup>TU Darmstadt, <sup>4</sup>Zhejiang University

2:40PM

2A.4

# Toward Automated Potential Primary Asset Identification in Verilog Designs

Subroto Nath and Benjamin Tan

University of Calgary

## **SESSION 2B**

## Wednesday April 23

# **Security-aware Design Flow for Integrated Circuits**

Chair: Tasnuva Farheen, Louisiana State University

1:40PM

2B.1

# FlexGuard: Dynamic Scoring & Stochastic Routing for Balanced Security-Performance in 3D NoCs

Mahdi Hasanzadeh<sup>1</sup>, Ebad Taheri<sup>2</sup>, Jason Green<sup>1</sup>, Abdolhossein Sarrafzadeh<sup>1</sup>, Ahmad Patooghy<sup>1</sup>

<sup>1</sup>North Carolina A & T State University, <sup>2</sup>Independent Researcher

2:00PM

2B.2

## **REDACTOR: eFPGA Redaction for DNN Accelerator Security**

Yazan Baddour, Ava Hedayatipour, Amin Rezaei California State University, Long Beach

2:20PM

2B.3

# Power and Area-Efficient ECC Processor with Sequential Recursive Polynomial Multiplier Implementation

Pruthvi Parate<sup>1</sup>, Alwin Shaju<sup>1</sup>, Vasanthi D R<sup>1</sup>, Madhav Rao<sup>2</sup>

<sup>1</sup>International Institute of Information Technology Bangalore, <sup>2</sup>International Institute of Information Technology-Bangalore

2:40PM

2B.4

# A PPA- and Security-aware Physical Design Flow

Chun-Wei Chiu and Ting-Chi Wang

National Tsing Hua University

3:00PM

2B.5

# The Impact of Logic Locking on Confidentiality: An Automated Evaluation

Lennart Reimann<sup>1</sup>, Evgenii Rezunov<sup>1</sup>, Dominik Germek<sup>2</sup>, Luca Collini<sup>3</sup>, Christian Pilato<sup>4</sup>, Ramesh Karri<sup>3</sup>, Rainer Leupers<sup>1</sup>

<sup>1</sup>RWTH Aachen University, <sup>2</sup>Corporate Research Robert Bosch GmbH, <sup>3</sup>NYU Tandon School of Engineering, <sup>4</sup>Politecnico di Milano

#### **SESSION 2C**

## Wednesday April 23

## Efficient Hardware Architectures for AI and Approximate Computing

Chair: Ahmedullah Aziz, The University of Tennessee, Knoxville

1:40PM

2C.1

# Efficient Self-Supervised Continual Learning with Progressive Task-correlated Layer Freezing

Li Yang<sup>1</sup>, Sen Lin<sup>2</sup>, Fan Zhang<sup>3</sup>, Junshan Zhang<sup>4</sup>, Deliang Fan<sup>5</sup>

<sup>1</sup>university of north carolina at charlotte, <sup>2</sup>University of Houston, <sup>3</sup>Johns Hopkins University, <sup>4</sup>University of California, Davis, <sup>5</sup>Arizona State University

2:00PM

2C.2

# Bitwise Systolic Array Architecture for Runtime-Reconfigurable Multi-precision Quantized Multiplication on Hardware Accelerators

Yuhao Liu<sup>1</sup>, Salim Ullah<sup>2</sup>, Akash Kumar<sup>2</sup>

<sup>1</sup>Technische Universitaet Dresden, <sup>2</sup>Ruhr-Universitaet Bochum

2:20PM

2C.3

# LibApprox: A Comprehensive Library for Performance Efficient Approximate Circuits

Bhargav D V<sup>1</sup>, Dantu Nandini Devi<sup>2</sup>, Rachana Kaparthi<sup>1</sup>, Madhav Rao<sup>1</sup>

<sup>1</sup>International Institute of Information Technology-Bangalore, <sup>2</sup>International Institute of Information Technology Bangalore

2:40PM

2C.4

# Meta-Heuristic Optimization for Designing Error Diluted Weight Stationary Approximate Systolic Array Architecture

Dantu Nandini Devi<sup>1</sup>, Bindu G Gowda<sup>2</sup>, Madhav Rao<sup>3</sup>

<sup>1</sup>International Institute of Information Technology Bangalore, <sup>2</sup>International Institute of Information Technology, Bangalore, <sup>3</sup>International Institute of Information Technology-Bangalore

3:00PM

2C.5

# Design of Hardware-Efficient Inexact Multiplier Using Evolutionary Algorithm Factored by Multi-variate Approximation

Dantu Nandini Devi<sup>1</sup>, Saketh Gajawada<sup>2</sup>, Madhav Rao<sup>3</sup>

<sup>1</sup>International Institute of Information Technology

Bangalore, <sup>2</sup>InternationalInstituteofInformationTechnologyBangalore, <sup>3</sup>International Institute of Information Technology-Bangalore

#### **SESSION PW1**

# Thursday April 24

## **Short Presentation & WIP Session 1**

Chair: Avani Dave, Intel Corp.

9:40AM

PW1.1

# Area-optimized 2D Interleaved Adder Tree Design for Sparse DCIM Edge Processing Akash Sankhe<sup>1</sup>, Mukul Lokhande<sup>1</sup>, Radheshyam Sharma<sup>1</sup>, Santosh Vishvakarma<sup>2</sup>

<sup>1</sup>Indian Institute of Technology Indore, <sup>2</sup>IIT Indore

9:45AM

PW1.2

# Hardware and Algorithm Codesign for Efficient Gaze Tracking in Virtual Reality System

Sai Qian Zhang, Wenxuan Liu, Haiyu Wang New York University 9:50AM

#### PW1.3

# Reinforcement Learning for Testtime Optimization in the Network-on-Chip based Systems

Anantha Ganesh Karikar Kamath<sup>1</sup>, Aditya Kulkarni<sup>2</sup>, Himanshu Singh<sup>2</sup>, Kanchan Manna<sup>3</sup> <sup>1</sup>BITS Pilani, Goa Campus, <sup>2</sup>Dept. of CSIS, BITS Pilani, Goa Campus, <sup>3</sup>Dept. of CSIS, BITS Pilani Goa Campus

9:55AM

#### PW1.4

# Efficient and Scalable Place and Route Methodology for Large-Scale Hierarchical Designs: Achieving Faster Turnaround Time and Predictability

Subhadeep Aich<sup>1</sup>, Rajanikant Sakariya<sup>2</sup>, Vivek Joshi<sup>1</sup>

<sup>1</sup>Texas Instruments, <sup>2</sup>Texas Instruments (India) Pvt. Ltd.

10:00AM

#### PW1.5

# Die Area Reduction by Decongesting Top Channels Using Novel Feedthrough Insertion Methodology in Hierarchical SoC Designs

Rajanikant Sakariya<sup>1</sup>, Subhadeep Aich<sup>1</sup>, Vivek Joshi<sup>1</sup>, Roger Griesmer<sup>2</sup>

<sup>1</sup>Texas Instruments (India) Pvt. Ltd., <sup>2</sup>Texas Instruments Incorporated

10:05AM

#### PW1.6

# DT2HDL: A Binary Decision Tree to HDL Generation tool

Qijia Tang, Dinesh Pamunuwa, Roshan Weerasekera University of Bristol

10:10AM

#### PW1.7

# Adding Context to LLM-Guided Verilog Repair

Abdelrahman Elnaggar and Benjamin Tan University of Calgary

10:15AM

#### **PW1.8**

# A Max Weighted-Matching based Non-Greedy Post-HLS Power Gating Technique with Comprehensive Power Modeling

Xiuyan Zhang and Shantanu Dutt University of Illinois at Chicago

10:20AM

## PW1.9

# Therunet-SP: 2.5D IC Thermal Simulation Using U-Net Convolution and Scaling Procedure

Yu-Min Lee, Shun-Ping Huang, Ying-Hui Lin National Yang Ming Chiao Tung University

10:25AM

## PW1.10

# MErBAG: Mesh Error Based Adaptive Grid Generation in System-Level Thermal Analysis

Yu-Min Lee, Shih-Chieh Hsu, Bo-Yi Tsai, Zong-Lin Lu National Yang Ming Chiao Tung University

## **SESSION PW2**

## **Thursday April 24**

#### **Short Presentation & WIP Session 2**

Chair: Hao Jiang, San Francisco State University

9:40AM

PW2.1

Illuminati: A Simulation Framework for Modeling and Evaluating Photonic Neural

**Networks**

Andy Wolff and Avinash Karanth Ohio University

9:45AM

PW2.2

**Evaluating LLM-based Communicative Agents for Verilog Design**

Parker Link and Benjamin Tan University of Calgary

9:50AM

PW2.3

Weighted Vertex Cover Using Disjoint Set Data Structures for the Memory Reconfiguration Problem

Rouwaida Kanj Synopsys

9:55AM

PW2.4

Guardians of the Quantum GAN

Archisman Ghosh<sup>1</sup>, Debarshi Kundu<sup>2</sup>, Avimita Chatterjee<sup>2</sup>, Swaroop Ghosh<sup>2</sup>

¹The Pennsylvania State University, ²Pennsylvania State University

10:00AM

#### PW2.5

Graphene-Based FPGA Design and Optimization at the 7nm FinFET Technology Node Sheng Lu<sup>1</sup>, Zhenlin Pei<sup>1</sup>, Liuting Shang<sup>2</sup>, Sungyong Jung<sup>3</sup>, Qilian Liang<sup>2</sup>, Chenyun Pan<sup>2</sup>

<sup>1</sup>The University of Texas at Arlington, <sup>2</sup>University of Texas at Arlington, <sup>3</sup>South Dakota State University

10:05AM

#### **PW2.6**

## **Function Approximation Using Analog Building Blocks in Flexible Electronics**

Paula Lozano Duarte<sup>1</sup>, Aradhana Dube<sup>1</sup>, Georgios Zervakis<sup>2</sup>, Mehdi Tahoori<sup>1</sup>, Sani Nassif<sup>3</sup> <sup>1</sup>Karlsruhe Institute of Technology, <sup>2</sup>University of Patras, <sup>3</sup>Radyalis

10:10AM

#### PW2.7

# Deep Learning-Based ASM-ESD Forward I-V Parameter Extraction

Fredo Chavez and Sourabh Khandelwal Macquarie University

10:15AM

#### PW2.8

# **Exploring Parallel Implementation of SPHINCS+ using Advanced Vector Extensions** (AVX) Sets

Yaoyun Zhou, Kavin Rajasekaran, QIAN WANG University of California, Merced

10:20AM

#### PW2.9

# **Cross-Layer EM Fault Injection Assessment Framework**

Hanqiu Wang<sup>1</sup>, Ruochen Dai<sup>1</sup>, Tuba Yavuz<sup>1</sup>, Xiaolong Guo<sup>2</sup>, Orlando Arias<sup>3</sup>, Dean Sullivan<sup>4</sup>, Siqi Dai<sup>1</sup>, Honggang Yu<sup>1</sup>, Michael Lee<sup>1</sup>, Domenic Forte<sup>1</sup>, Shuo Wang<sup>1</sup>

<sup>1</sup>University of Florida, <sup>2</sup>Electrical and Computer Engineering Department, Kansas State University, <sup>3</sup>University of Massachusetts Lowell, <sup>4</sup>University of New Hampshire

10:25AM

PW2.10

#### **Adversarial Assertions**

Prabhat Mishra

University of Florida

#### **SESSION PW3**

## **Thursday April 24**

#### **Short Presentation & WIP Session 3**

Chair: Sushant Sadangi, Intel Corporation

9:40AM

PW3.1

# Optimizing Post-quantum Crypto Algorithms in Embedded IoT Systems with QUIC Protocol

Ben Dong and QIAN WANG University of California, Merced

9:45AM

PW3.2

# Analysis of the Impact of LFSR Architecture on Accuracy of Stochastic Computing Processors

Seongmo An, Sangho Lee, Jinyoung Shin, Yue Ri Jeong, Seung Eun Lee Seoul National University of Science and Technology

9:50AM

**PW3.3**

# Aging Attack on Systolic Array-based AI accelerators via NBTI-Induced Aging

Masoud Heidary and Biresh Kumar Joardar

University of Houston

9:55AM

## PW3.4

# Analysis of Short and Aging Faults in TSVs at the Physical Level with Parametric Variation

Prosen Kirtonia<sup>1</sup>, Shelby Williams<sup>1</sup>, Prasanna Kawatker<sup>1</sup>, Kasem Khalil<sup>2</sup>, Magdy Bayoumi<sup>3</sup>

<sup>1</sup>University of Louisiana at Lafayette, <sup>2</sup>University of Mississippi, <sup>3</sup>U. of Louisiana

10:00AM

#### PW3.5

# **Energy-Aware DNN Task Scheduling with Dynamic Batching and Frequency Adjustment**

Vasileios Pentsos<sup>1</sup>, Spyros Tragoudas<sup>2</sup>, Kiriti Gowda<sup>3</sup>, Mike Schmit<sup>3</sup>

<sup>1</sup>Southern Illinois University of Carbondale, <sup>2</sup>Southern Illinois University Carbondale, <sup>3</sup>Advanced Micro Devices, Inc.

10:05AM

## **PW3.6**

## LUTAccel: Look-up-Table based Vector Systolic Accelerator on FPGAs

Aashish Tiwary<sup>1</sup>, Saketh Gajawada<sup>2</sup>, Jay Shah<sup>3</sup>, Nanditha Rao<sup>4</sup>

<sup>1</sup>International Institute of Information Technology,

Bangalore, <sup>2</sup>InternationalInstituteofInformationTechnologyBangalore, <sup>3</sup>International Institute of Information Technology Bangalore, <sup>4</sup>IBM

10:10AM

#### PW3.7

# RL-Driven Fine-Grained Power Gating for Modern Processors Using Multi-Layer Perceptron Models

Naman Kalra and Jaynarayan Tudu

IIT Tirupati

10:15AM

## PW3.8

# RECminThrash: Recency and Eviction Count Based Cache Replacement Policy to Minimize Thrashing at the Last Level Caches

Chetan Kumar<sup>1</sup> and Arijit Nath<sup>2</sup>

<sup>1</sup>Indian Institute of Information Technology, Guwahati, <sup>2</sup>IIIT Guwahati

10:20AM

## PW3.9

# Precision Unwound: Fine-Tuning Loop Unrolling for Energy-efficient FPGA-based PQC using HLS

Srijeet Guha<sup>1</sup> and Andrea Guerrieri<sup>2</sup>

<sup>1</sup>Nvidia, <sup>2</sup>EPFL and HES-SO

10:25AM

#### PW3.10

# Assertion-Based Trojan Localization Using Iterative Path Sensitization

Suriya Srinivasan, Ranga Vemuri, Andrew Jones, Cameron Hingson, Gannon Darrach University of Cincinnati

## **SESSION 3A**

#### **Thursday April 24**

## Simulation and Analysis in VLSI Design

Chair: Srini Krishnamoorthy, Intel Corporation

10:45AM

3A.1

**DAPP: Delay Aware Power Prediction**

Sagar Satapathy and Dip Sankar Banerjee Indian Institute of Technology Jodhpur

11:05AM

3A.2

Thermal Model Extraction at Chip Boundaries for Thermal Simulation of Chip in a System

Kai-Xiang Lin, Yu-Min Lee, Bo-Yi Tsai National Yang Ming Chiao Tung University

11:25AM

3A.3

Analysis of VF-TLP ESD Measurements Using Machine Learning

Seyed Hossein Hosseini<sup>1</sup>, Mehrdad Nourani<sup>1</sup>, Theo Smedes<sup>2</sup>, Charvaka Duvvury<sup>3</sup>

<sup>1</sup>The University of Texas at Dallas, <sup>2</sup>NXP Semiconductors, <sup>3</sup>iT2 Technologies

11:45AM

3A.4

**Machine Learning-Based Pruning Algorithm of Partitioning Techniques for Circuit Simulation**

Qian Chen, Xiaofeng Yang, Shengli Lu Southeast University

## **SESSION 3B**

## **Thursday April 24**

## **Recent Trends in Cognitive Computing Hardware**

Chair: Hongyu An, Michigan Technological University

10:45AM

3B.1

# **Explainable AI-Guided Efficient Approximate DNN Generation for Multi-Pod Systolic Arrays**

Ayesha Siddique<sup>1</sup>, Khurram Khalil<sup>1</sup>, Khaza Anuarul Hoque<sup>2</sup> <sup>1</sup>University of Missouri-Columbia, <sup>2</sup>University of Missouri

11:05AM

3B.2

# PhotoGAN: Generative Adversarial Neural Network Acceleration with Silicon Photonics

Tharini Suresh, Salma Afifi, Sudeep Pasricha Colorado State University

11:25AM

3B.3

# **Keep All in Memory with Maxwell: a Near-SRAM Computing Architecture for Edge Al Applications**

Gregoire Eggermann<sup>1</sup>, Giovanni Ansaloni<sup>1</sup>, David Atienza<sup>2</sup>

<sup>1</sup>EPFL, <sup>2</sup>École Polytechnique Fédérale de Lausanne (EPFL)

11:45AM

3B.4

# Efficient digital architecture of spiking encoders for neuromorphic accelerators

Ruizhe Li, Muhammad Farhan Azmine, Gauri Sharma, Yang Yi Virginia Tech

### 12:05PM

### 3B.5

### Region Masking to Accelerate Video Processing on Neuromorphic Hardware

Sreetama Sarkar<sup>1</sup>, Sumit Shrestha<sup>2</sup>, Yue Che<sup>1</sup>, Leobardo E Campos Macias<sup>2</sup>, Gourav Datta<sup>3</sup>, Peter Beerel<sup>4</sup>

<sup>1</sup>University of Southern California, <sup>2</sup>Intel Labs, <sup>3</sup>Case Western Reserve University, <sup>4</sup>Univ. of Southern California

#### **SESSION 3C**

### **Thursday April 24**

### Neuromorphic Computing for Next-gen Machine Intelligence

Chair: Kang Bai, AFRL

10:45AM

3C.1

# **Energy-Efficient Neuromorphic Closed-Loop Modulation System for Parkinson's Disease**

Ananna Biswas, Md Akhtaruzzaman, Hongyu An Michigan Technological University

11:05AM

3C.2

## Compressed CNN for Inferring Rapid RF Fingerprints using Memristor Crossbar Array

Josh Li<sup>1</sup>, Jianbin Huang<sup>2</sup>, Michael Jiang<sup>3</sup>, Kang Jun Bai<sup>4</sup>

<sup>1</sup>University of Maryland Baltimore County, <sup>2</sup>San Francisco State University, <sup>3</sup>University of Illinois Urbana-Champaign, <sup>4</sup>Air Force Research Laboratory

11:25AM

3C.3

### Modular Approach for Controlling Multi-Agent Systems with Natural Language

Christian Brazeau

Air Force Research Lab Information Directorate (AFRL/RITB)

11:45AM

3C.4

# **R2CTA:** Reinforcement Learning and Reservoir Computing based Chiplets TSV Assignment

Xiaomeng Wang and Cindy Yang Yi

Virginia Tech

#### **SESSION 4A**

### **Thursday April 24**

### **VLSI Physical Design Methodologies**

Chair: Chidhambaranathan Rajamanikkam, Synopsys Inc.

2:10PM

4A.1

Obstacle-aware Synthesis of the Bus Topology Considering Wire Length Minimization

Meng Lian<sup>1</sup>, Yushen Zhang<sup>1</sup>, Mengchu Li<sup>1</sup>, Tsun-Ming Tseng<sup>1</sup>, Shejun Sun<sup>2</sup>, Ulf Schlichtmann<sup>1</sup>

<sup>1</sup>Technical University of Munich, <sup>2</sup>Huawei Device Co., Ltd

2:30PM

4A.2

A Comprehensive Approach to Characterizing VT Miscorrelation Derates for Physical Design and Timing Signoff

Pravin Chandran, Hitesh Sharma, Srinivas Bodapati Intel

2:50PM

4A.3

**Open-ALOE:** An Analog Layout Automation Flow for the Open-Source Ecosystem Yueting Li<sup>1</sup>, Xingyu Ni<sup>2</sup>, Sara Achour<sup>2</sup>, Boris Murmann<sup>3</sup>

<sup>1</sup>University of California, Berkeley, <sup>2</sup>Stanford University, <sup>3</sup>University of Hawaii, Mānoa

3:10PM

4A.4

Improving Routability Prediction via NAS Using a Smooth One-shot Augmented Predictor

Arjun Sridhar, Chen-Chia Chang, Junyao Zhang, Yiran Chen Duke university

#### **SESSION 4B**

### **Thursday April 24**

### **Security Evaluation in Complex Designs**

Chair: Tasnuva Farheen, Louisiana State University

2:10PM

4B.1

# Genetic Algorithm-Assisted Golden-Free Standard Cell Library Extraction from SEM Images

Mengdi Zhu, Ronald Wilson, Reiner Dizon-Paradis, Olivia Dizon-Paradis, Domenic Forte, Damon Woodard

University of Florida

2:30PM

4B.2

### A Framework for PCB Design File Reconstruction from X-ray CT Annotations

Carson Sobolewski, David Koblah, Domenic Forte University of Florida

2:50PM

4B.3

# i-Know What You Do: Privacy Evaluation of Apple Smartphones with Remote Acoustic Side-Channels

Oswa Amro, Sanapala Jaswanth, Sai Dishanth Banoth, Urbi Chatterjee Indian Institute of Technology Kanpur

3:10PM

4B.4

### ML-based Real-Time URL Inspection with Hardware Acceleration for Enhanced Web Security

Majid Nezarat<sup>1</sup>, Erfan Khedersolh<sup>1</sup>, Hadi Shahriar Shahhosseini<sup>1</sup>, Amin Rezaei<sup>2</sup>

<sup>1</sup>Iran University of Science and Technology, <sup>2</sup>California State University, Long Beach

3:30PM

4B.5

# MATTER: MULTI-STAGE ADAPTIVE THERMAL TROJAN FOR EFFICIENCY & RESILIENCE DEGRADATION

Mehdi Elahi<sup>1</sup>, Mohamed R.Elshamy<sup>2</sup>, Abdel-Hameed Badawy<sup>2</sup>, Mahdi Fazeli<sup>3</sup>, Ahamd Patooghy<sup>1</sup>

<sup>1</sup>North Carolina A&T state University, <sup>2</sup>New Mexico state university, <sup>3</sup>Halmstad University

#### **SESSION 4C**

### **Thursday April 24**

### **Generative AI on Edge**

Chair: Amey Kulkarni, NVIDIA

2:10PM

4C.1

# MambaLiteSR: Image Super-Resolution with Low-Rank Mamba using Knowledge Distillation

Romina Aalishah, Mozhgan Navardi, Tinoosh Mohsenin Johns Hopkins University

2:30PM

4C.2

# State of Hardware Fuzzing: Current Methods and the Potential of Machine Learning and Large Language Models

Kevin Immanuel Gubbi<sup>1</sup>, Mohammadnavid Tarighat<sup>2</sup>, Arvind Sudarshan<sup>2</sup>, Inderpreet Kaur<sup>1</sup>, Pavan Dheeraj Kota<sup>2</sup>, Avesta Sasan<sup>1</sup>, Houman Homayoun<sup>2</sup>

<sup>1</sup>University of California, Davis, <sup>2</sup>University of California Davis

2:50PM

4C.3

# Dynamic Partial Reconfiguration of FPGAs for Energy-Efficient Machine Learning Inference in IoT Systems

Ethan Chen, Junting Deng, Chia Jen Cheng, Jiachen Xu, John Kan, Yuyi Shen, Vanessa Chen Carnegie Mellon University

3:10PM

4C.4

# Leveraging Generative AI for Platform Hardware Design Automation - Learnings and Recommendations

Srini Krishnamoorthy Intel Corp.

#### **SESSION 5A**

#### Friday April 25

### Memristive and Charge-Trap Devices for Next-Gen Computing

Chair: Sushant Sadangi, Intel Corporation

8:40AM

5A.1

### Behavioral Model of Charge-Trap Transistors for Neuromorphic Systems

Ataollah Saeed Monir<sup>1</sup>, Navid Rezazadeh<sup>2</sup>, John Gosson<sup>2</sup>, Boris Vaisband<sup>3</sup>

<sup>1</sup>McGill university, <sup>2</sup>Blumind, <sup>3</sup>University of California, Irvine

9:00AM

5A.2

### All-Optical Reconfigurable Activation Function based on Saturable Absorption

Oceane Destras<sup>1</sup>, Felipe Gohring de Magalhaes<sup>2</sup>, Sébastien Le Beux<sup>3</sup>, Gabriela Nicolescu<sup>2</sup> <sup>1</sup>Polytechnique Montreal, <sup>2</sup>Polytechnique Montréal, <sup>3</sup>Concordia University

9:20AM

5A.3

# Formal Verification of Error Bounds for Resistive-Switching-based Multilevel Matrix-Vector Multipliers

Kemal Çağlar Coşkun<sup>1</sup>, Chandan Kumar Jha<sup>2</sup>, Muhammad Hassan<sup>3</sup>, Rolf Drechsler<sup>4</sup>

<sup>1</sup>Institute of Computer Science, University of Bremen, <sup>2</sup>University of Bremen, <sup>3</sup>Institute of Computer Science, University of Bremen / DFKI, <sup>4</sup>University of Bremen/DFKI

9:40AM

5A.4

# Robust and Efficient NAND-like TST-MRAM with Parallel Write/Read Operations and Reconfigurable PUF Mode

Songhan Zhang, Xianzeng Guo, Yaling Wang, Chao Wang, Bi Wang, Zhaohao Wang Beihang University 10:00AM

#### 5A.5

### A Novel Full Adder Design Using Hybrid Memristor Ratioed Logic

Hussein Fadlallah<sup>1</sup>, Rouwaida Kanj<sup>2</sup>, Basma Hajri<sup>3</sup>

<sup>1</sup>American University of Beirut, <sup>2</sup>Synopsys, <sup>3</sup>Qualcomm

#### **SESSION 5B**

#### Friday April 25

### AI-Driven Embedded Computing and Power-Aware System Design

Chair: Srini Krishnamoorthy, Intel Corporation

8:40AM

5B.1

### V-SYNC-Aware GPU DVFS Governor for Efficient Game Application Execution on Mobile Devices

En-Ming Huang<sup>1</sup>, Yu-Fu Kao<sup>2</sup>, Yan-Hong Lu<sup>2</sup>, Chun-Yi Lee<sup>3</sup>

<sup>1</sup>Google, Inc./National Taiwan University, <sup>2</sup>Google, Inc., <sup>3</sup>Department of Computer Science

and Information Engineering, National Taiwan University

9:00AM

5B.2

### **Energy-Efficient QoS-Aware Scheduling for S-NUCA Many-Cores**

Sudam Wasala<sup>1</sup>, Jurre Wolff<sup>1</sup>, Yixian Shen<sup>1</sup>, Anuj Pathania<sup>1</sup>, Clemens Grelck<sup>2</sup>, Andy Pimentel<sup>1</sup>

<sup>1</sup>University of Amsterdam, <sup>2</sup>Friedrich Schiller University Jena

9:20AM

#### 5B.3

# Deep Neural Network Inference Partitioning in Embedded Hybrid Analog-Digital Systems

Fabian Kreß<sup>1</sup>, Julian Hoefer<sup>2</sup>, Qiushi Lin<sup>3</sup>, Patrick Schmidt<sup>2</sup>, Zhenhua Zhu<sup>3</sup>, Yu Zhu<sup>3</sup>, Tanja Harbaum<sup>4</sup>, Yu Wang<sup>3</sup>, Juergen Becker<sup>1</sup>

$^1\mathrm{Karlsruhe}$  Institute of Technology - ITIV,  $^2\mathrm{Karlsruhe}$  Institute of Technology,  $^3\mathrm{Tsinghua}$  University,  $^4\mathrm{KIT}$

9:40AM

#### 5B.4

# Real-time Thermal Map Characterization and Analysis for Commercial GPUs with AI Workloads

Jincong Lu<sup>1</sup>, Sachin Sachdeva<sup>1</sup>, Yuxuan Lin<sup>2</sup>, Sheldon Tan<sup>3</sup>

<sup>1</sup>University of California, Riverside, <sup>2</sup>The Overlake School, <sup>3</sup>University of California at Riverside

10:00AM

#### 5B.5

# IMU-based Motion Trajectory Reconstruction and Recognition with Dynamic Calibration on Embedded System Platform

Kai-Po Hsu<sup>1</sup>, Tsung-Han Lai<sup>1</sup>, Yi-Ting Li<sup>1</sup>, Wuqian Tang<sup>1</sup>, Yun-Ju Lee<sup>2</sup>, Yung-Chih Chen<sup>3</sup>, Wen-Hsin Chiu<sup>1</sup>, Chun-Yao Wang<sup>1</sup>

<sup>1</sup>National Tsing Hua University, <sup>2</sup>National Tsing-Hua University, <sup>3</sup>National Taiwan University of Science and Technology

#### **SESSION 5C**

#### Friday April 25

### Design Innovation and Accelaration in the Nanometer Era

Chair: Rasit Onur Topaloglu, Adeia

8:40AM

5C.1

### **Ternary-valued Associative Processor Design**

Mira Hout<sup>1</sup>, Rouwaida Kanj<sup>2</sup>, Ahmed Eltawil<sup>3</sup>, Mohammed Fouda<sup>4</sup>

<sup>1</sup>ECE Dept., American University of Beirut,, <sup>2</sup>Synopsys, <sup>3</sup>King Abdullah University of Science and Technology, <sup>4</sup>Rain Neuromorphics Inc.

9:00AM

5C.2

### A Time-Borrowing Method for High-Performance Bundled-Data Asynchronous Circuits

Bohan Wang, Zeyang Xu, Lingfeng Zhou, Huiyao Wang, Jinghai Wang, Zhiyi Yu, Shanlin Xiao

Sun Yat-Sen University

9:20AM

5C.3

## Machine Learning Assisted Magnetic-core Coupled Inductor Design for Interleaved Buck Converter

Maliha Elma, Navya Goli, Umamaheswara Tida North Dakota State University

9:40AM

5C.4

# A Modified RC and Delay based ESD Clamp Circuit with False-trigger Immunity during normal supply operation.

Naresh Kumar, Divya Agarwal, Rajesh Narwal STMicroelectronic

#### **SESSION 6A**

#### Friday April 25

### Advances in Quantum Computing: Security, Optimization, and AI Integration

Chair: Srini Krishnamoorthy, Intel Corporation

10:30AM

6A.1

### Watermarking of Quantum Circuits

Rupshali Roy and Swaroop Ghosh Pennsylvania State University

10:50AM

6A.2

### Optimizing Quantum Embedding using Genetic Algorithm for QML Applications

Koustubh Phalak<sup>1</sup>, Archisman Ghosh<sup>2</sup>, Swaroop Ghosh<sup>1</sup>

<sup>1</sup>Pennsylvania State University, <sup>2</sup>The Pennsylvania State University

11:10AM

6A.3

### **Quantum Prometheus: Defying Overhead with Recycled Ancillas in Quantum Error Correction**

Avimita Chatterjee<sup>1</sup>, Archisman Ghosh<sup>2</sup>, Swaroop Ghosh<sup>1</sup>

<sup>1</sup>Pennsylvania State University, <sup>2</sup>The Pennsylvania State University

11:30AM

6A.4

### AI-driven Reverse Engineering of QML Models

Archisman Ghosh<sup>1</sup> and Swaroop Ghosh<sup>2</sup>

<sup>1</sup>The Pennsylvania State University, <sup>2</sup>Pennsylvania State University

#### **SESSION 6B**

### Friday April 25

### **Advanced Signal Processing and AI Acceleration**

Chair: Rasit Onur Topaloglu, Adeia

10:30AM

6B.1

### Accelerating Reliability Analysis for Aging and Self-heating using Machine Learning

Tarek Mohamed<sup>1</sup> and Hussam Amrouch<sup>2</sup>

<sup>1</sup>Semiconductor Test and Reliability (STAR), University of Stuttgart, Stuttgart, Germany., <sup>2</sup>Technical University of Munich (TUM)

10:50AM

6B.2

## A Generalized Hardware-Efficient Gabor Wavelet Architecture for Medical Image Processing

Priyanka Agarwal<sup>1</sup>, Pruthvi Parate<sup>2</sup>, Madhav Rao<sup>3</sup>

<sup>1</sup>IIIT Bangalore, <sup>2</sup>International Institute of Information Technology Bangalore, <sup>3</sup>International Institute of Information Technology-Bangalore

11:10AM

6B.3

# Notch filter based Readout Interface for Hall-effect sensors for DC and High-Frequency Currents

Ayesha Hassan, Aireen Amir Jalal, Asma Mahar, Alan Mantooth University of Arkansas

11:30AM

6B.4

## Piecewise-Linear Approximation of Self-Attention and Its Accuracy-Aware Training for Area-Efficient Vision Transformer Inference Accelerator

Teppei Kawamura, Yutaka Masuda, Tohru Ishihara Nagoya University

#### **SESSION 6C**

#### Friday April 25

### **Intelligent and Secure Computing for Next-Gen Systems**

Chair: Hossein Sayadi, California State University, Long Beach

10:30AM

6C.1

# **Energy-efficient Persistently Secure Block-based Differential Checkpointing for Energy Harvesting Devices**

Shyamala Palanisamy<sup>1</sup>, Wei Wei<sup>2</sup>, Mimi Xie<sup>3</sup>

<sup>1</sup>University of Texas at San Antonio, <sup>2</sup>UTSA, <sup>3</sup>The University of Texas at San Antonio

10:50AM

6C.2

# **Energy-Adaptive Checkpoint-Free Intermittent Inference for Low Power Energy Harvesting Systems**

Sahidul Islam, Wei Wei, Jishnu Banerjee, Chen Pan

The University of Texas at San Antonio

11:10AM

6C.3

### Efficient Object Detection from Fused RGB and IR Aerial Images Enhanced by Token Selection

Raghavendra Chitroju Kodanda Saiayyappa, Tanvi Banerjee, Wen Zhang wright state university

11:30AM

6C.4

# Obfuscation-Resistant Hardware Malware Detection: A Stacked Denoising Autoencoder Approach

Zhangying He, Chelsea Fernandes, Hossein Sayadi

California State University, Long Beach

11:50AM

6C.5

### Navigating the Trilemma: Security, Power, and Performance Trade-offs in Bluetooth Low Energy

Ning Miao<sup>1</sup>, Chongzhou Fang<sup>1</sup>, Ruijie Fang<sup>1</sup>, Ruoyu Zhang<sup>1</sup>, Mahdi Eslamimehr<sup>2</sup>, Setareh Rafatirad<sup>3</sup>, Hossein Sayadi<sup>4</sup>, Houman Homayoun<sup>3</sup>

<sup>1</sup>University of California, Davis, <sup>2</sup>University of California, Los Angeles, <sup>3</sup>University of California Davis, <sup>4</sup>California State University, Long Beach

#### **SESSION 7B**

#### Friday April 25

### Optimizing Memory, Power, and Computation for Next-Gen Systems

Chair: Murthy Palla, Synopsys Inc.

12:55PM

**7B.1**

### **Exploiting The Presence of Abundant Zero Data to Improve NVM Lifespan**

Arijit Nath and Harsh Raj

IIIT Guwahati

1:15PM

7B.2

### **Battery State of Health Estimation Using LLM Framework**

Aybars Yunusoglu<sup>1</sup>, Dexter Le<sup>2</sup>, Karn Tiwari<sup>3</sup>, Murat Isik<sup>4</sup>, I. Can Dikmen<sup>5</sup>, Teoman Karadag<sup>5</sup>

<sup>1</sup>Purdue University, <sup>2</sup>Drexel University, <sup>3</sup>Indian Institute of Science, Bangalore, <sup>4</sup>Stanford University, <sup>5</sup>Temsa Research & Development Center

1:35PM

**7B.3**

## SPEED: Scalable and Predictable EnhancEments for Data Handling in Autonomous Systems

Dongjoo Seo<sup>1</sup>, Changhoon Sung<sup>2</sup>, Junseok Park<sup>3</sup>, Ping-Xiang Chen<sup>1</sup>, Bryan Donyanavard<sup>2</sup>, Nikil Dutt<sup>1</sup>

<sup>1</sup>University of California, Irvine, <sup>2</sup>San Diego State University, <sup>3</sup>Kookmin University

1:55PM

**7B.4**

### An FPGA-based Emulation Process for Dynamic Quantum Circuits

Yicheng Song and Zeljko Zilic McGill University

2:15PM

**7B.5**

# **Sharp-Edge: A Robust Edge Computing Solution through Performance Monitoring Using Tiny Machine Learning**

Mehdi Amininasab<sup>1</sup>, Mahdi Fazeli<sup>2</sup>, Ahmad Patooghy<sup>3</sup>

<sup>&</sup>lt;sup>1</sup>Independent Scholar, <sup>2</sup>Halmstad University, <sup>3</sup>North Carolina A&T State University

#### **SESSION 7C**

#### Friday April 25

### **Hardware Techniques in Quantum Computing Security**

Chair: Yuntao Liu, Lehigh University

12:55PM

7C.1

# **Quantum Quandaries: Unraveling Encoding Vulnerabilities in Quantum Neural Networks**

Suryansh Upadhyay<sup>1</sup> and Swaroop Ghosh<sup>2</sup>

<sup>1</sup>Penn State University, <sup>2</sup>Pennsylvania State University

1:15PM

7C.2

### **Stealthy Conditional Trojans in Quantum Circuits**

Jayden John, Lakshaman Golla, QIAN WANG University of California, Merced

1:35PM

7C.3

### **OPAQUE: Obfuscating Phase in Quantum Circuit Compilation for Efficient IP Protection**

Anees Rehman<sup>1</sup>, Vincent Langford<sup>2</sup>, Jayden John<sup>3</sup>, Yuntao Liu<sup>2</sup>

<sup>1</sup>Independent, <sup>2</sup>Lehigh University, <sup>3</sup>UC Merced

1:55PM

7C.4

### **Exploration of Vulnerabilities of Fault-Tolerant Quantum Computing**

Theodoros Trochatos<sup>1</sup>, Christopher Kang<sup>2</sup>, Frederic Chong<sup>2</sup>, Jakub Szefer<sup>3</sup>

<sup>1</sup>Yale University, <sup>2</sup>University of Chicago, <sup>3</sup>Northwestern University

### CALL FOR PAPERS

### 27<sup>th</sup> International Symposium on

# **QUALITY ELECTRONIC DESIGN**

April 2026. Santa Clara, CA

Paper Submission Deadline: Sept. 9, 2025 **Acceptance Notifications: Dec. 5, 2025** Final Camera-Ready paper: Jan. 10, 2026

A pioneer and leading interdisciplinary electronic design and semiconductor conference ISQED accepts and promotes papers in following areas:

- IoT and Cyber-Physical systems

- **Cognitive Computing in Hardware**

- IP Design, quality, interoperability and reuse

- Advanced 3D ICs & 3D Packaging

- FPGA Architecture, Design, and CAD

- Robust & Power-conscious Circuits & Systems

- Advanced & 3D IC Packaging Technology

- **Hardware Security**

- \*\* **PCB and PWB Technology & Manufacturing**

- Circuit & System Design

- \*\* **EDA Methodologies, Tools, Flows**

- Semiconductor & Nano Technology

- • **Test & Verification**

- **Design for Test**

SQED papers have been published in IEEE Xplore and conference proceedings and indexed in Scopus and El.

IC Design & Test Resources & Logistics

www.Innovotek.com