Vehireles, Quaintum Computing

# Final Program

2024 25<sup>th</sup> International Symposium on

# QUALITY ELECTRONIC DESIGN

April 3-5, 2024

Seven Hills Conference Center

San Francisco State University

San Francisco, CA US

International Society for Quality Electronic Design Copyright© ISQED. All rights reserved. www.ISQED.com

### **Corporate Sponsors**

### **Technical Sponsors**

ISQED'24 is produced and sponsored by the International Society for Quality Electronic Design Copyright © 2024 All rights reserved

### **WELCOME TO ISQED'24**

It is with great enthusiasm that we, on behalf of the ISQED conference and technical committees, extend a warm welcome to all attendees of the 25th anniversary of the International Symposium on Quality Electronic Design (ISQED'24). This year, we commemorate a quarter-century of innovation, leadership, and continuous dialogue on the crucial role of Quality Electronic Design (QED) in navigating the complexities of modern semiconductor technologies.

Embracing the spirit of inclusivity and accessibility, ISQED'24 continues to adopt a hybrid format, combining the best of inperson engagement with the flexibility of virtual participation. This approach allows us to convene at the esteemed Seven Hills Conference Center at San Francisco State University, located at 800 Font Blvd, San Francisco, CA 94132, while extending our reach to a global audience.

Over the past 25 years, ISQED has emerged as a vanguard in advocating for QED principles, contributing significantly to the advancement of semiconductor technology design. As we celebrate this landmark anniversary, ISQED'24 is dedicated to furthering this legacy, offering an expansive program featuring keynotes, panels, tutorials, and more than 100 peer-reviewed papers that echo our commitment to excellence in electronic design.

This year's symposium is supported by the technical sponsorship of esteemed IEEE societies—namely, the Electron Devices Society, and the Circuits and Systems Society—as well as the collaboration with ACM/SigDA. Reflecting our ongoing commitment to scholarly excellence, all conference proceedings and papers will be made available in the IEEE Xplore digital library and indexed by Scopus.

ISQED'24 is tailored to address the pivotal trends that are shaping the future of our industry, including Al/ML, Autonomous Vehicles, Security, IoT, and Quantum Computing. Our curated program encompasses two keynote speeches, embedded tutorials, a panel discussion, and a multitude of peer-reviewed technical papers, spotlighting emerging innovations in electronic circuit and system design, automation, testing, verification, and beyond.

The enthusiasm and quality of submissions for this year's conference have been exceptional, leading to a two and a half-day technical program that features four parallel sessions. Over 100 peer-reviewed papers will be presented, highlighting cutting-edge developments across various domains, including sensors, security, semiconductor technologies, and cyber-physical systems. Adhering to our hybrid format, all technical presentations, plenary sessions, panel discussions, and tutorials will be accessible both in-person and virtually, ensuring a comprehensive and inclusive experience for all participants from April 3-5, Pacific Daylight Time (PDT).

We are profoundly grateful to our corporate sponsors, Innovotek and Silicon Valley Polytechnic Institute, for their generous support, which has been crucial in bringing the vision of ISQED'24 to life. Their contribution not only facilitates this year's conference but also nurtures the future of quality electronic design.

Welcome to ISQED'24—where tradition meets innovation at the crossroads of a shared vision for a future defined by excellence in electronic design.

**General Chair Cindy Yi** Virginia Tech

**Special Sessions Co-Chair** *Mimi Xie*The University of Texas at San Antonio

Panels Chair Ahmedullah Aziz The University of Tennessee, Knoxville Tutorials Chair Zhen Zhou Intel Corporation

Hossein Savadi

Publication Chair

Paul Wesling

Hewlett Packard (retired)

**Technical Program Chair**

California State University, Long Beach

**Technical Program Co- Chair Deliang Fan**Arizona State University

Tutorials Co-Chair Hechen Wang Intel Corporation

**ISQED Founder & Chair Ali A. Iranmanesh** Silicon Valley Polytechnic Institute

### **ISQED'24 Best Papers**

#### 3A.2

# Toward Early Stage Dynamic Power Estimation: Exploring Alternative Machine Learning Methods and Simulation Schemes

Philipp Fengler\*†, Sani Nassif†‡, Ulf Schlichtman\*

\*Chair of Electronic Design Automation; †Institute for Advanced Study,

†Technical University of Munich, Germany

#### 5A.5

# Reprogrammable Time-Domain RRAM Based Vector Matrix Multiplier for In-Memory Computing

Bipul Boro, Rushik Parmar, Ashvinikumar Dongre, Gaurav Trivedi Indian Institute of Technology Guwahati, Assam, India

#### 5B.1

# AutoAnnotate: Reinforcement Learning based Code Annotation for High Level Synthesis

Hafsah Shahzad\*, Ahmed Sanaullah†, Sanjay Arora†,

Uli Drepper†, Martin Herbordt\*

\*ECE Dept., Boston University †Red Hat, Inc.

#### 6B.1

# EASI-CiM: Event-driven Asynchronous Stream-based Image Classifier with Compute-in-Memory Kernels

Rahul Sreekumar<sup>1</sup>, Minseong Park<sup>1</sup>, Mohammad Nazmus Sakib<sup>1</sup>, Bhupendra Singh Reniwal<sup>2</sup>, Kyusang Lee1, Mircea R Stan<sup>1</sup>

<sup>1</sup>University of Virginia, <sup>2</sup>Indian Institute of Technology Jodhpur

Authors of best papers are acknowledged during the morning plenary session on Wednesday April 3. ISQED'24 best papers are sponsored by Silicon Valley Polytechnic Institute.

## **ISQED'24 Organizing Committee**

Program Chair

Hossein Sayadi

California State University

California State University, Long Beach

**Tutorials Co-Chair Hechen Wang** Intel Corporation

**General Chair Cindy Yi** Virginia Tech Program Co-Chair Deliang Fan

Arizona State University

Panel Chair Ahmedullah Aziz

The University of Tennessee,

Knoxville

Publication Chair Paul Wesling

Hewlett Packard (Retired)

**Tutorials Chair Zhen Zhou** Intel Corporation

**Special Sessions Chair**

Mimi Xie

The University of Texas at San Antonio

Plenary Chair Ali A. Iranmanesh

Silicon Valley Polytechnic Institute

### TECHNICAL PROGRAM COMMITTEES

**Cognitive Computing Hardware (CCH)**

Caiwen Ding, University of Connecticut (Chair)

Zhen Zhou, Intel Corp (Co-Chair)

**Committee Members:**

Divya Akella Kamakshi - NVIDIA Hongyu An - Michigan Technological University Kang Jun Bai - Air Force Research Laboratory Weidong Cao - The George Washington University

ong Cao - The George Washington Universit Gourav Datta - Amazon Deliang Fan - Johns Hopkins University

Haowen Fang - Synopsys Doo Seok Jeong - Hanyang University

Hao Jiang - San Francisco State University

Mehdi Kamal - University of Southern California Xiaolong Ma - Clemson University

Xiaolong Ma - Clemson University Gopal Raut - CDAC Bangalore

Ao Ren - Chongqing University

Ishan Thakkar - University of Kentucky Dongkuan Xu - North Carolina State University

igkuan Xu - North Carolina State University Cindy Yang Yi - Virginia Tech

Miao Yin - University of Texas at Arlington

Geng Yuan - University of Georgia

#### **Design Test and Verification (DTV)**

Deepashree Sengupta, Synopsys Inc. (Chair) Chidhambaranathan Rajamanikkam, Synopsys (Co-Chair)

**Committee Members:**

George Alexiou - Univ. Of PATRAS Serge Demidenko - Sunway University

Deliang Fan - Arizona State University Patrick Girard - LIRMM / CNRS

Chrysovalantis Kavousianos - Department of Computer Science and Engineering, University of Ioannina

Dimitris Nikolos - University of Patras Ernesto Sanchez - Politecnico di Torino Yiorgos Tsiatouhas - University of Ioannina Miroslav Velev - Aries Design Automation

**Arnaud Virazel - LIRMM**

### TECHNICAL PROGRAM COMMITTEES

(continued)

#### Electronic Design Automation Tools and Methodologies (EDA)

Srinivas Katkoori, University of South Florida (Chair) Srini Krishnamoorthy, Intel Corp. (Co-Chair)

**Committee Members:** Abishai Daniel - Micron **Dhruva Ghai - ORIENTAL UNIVERSITY INDORE** Zhong Guan - UC Santa Barbara

Xinfei Guo - Shanghai Jiao Tong University Sandeep Hari - Uhnder Inc

Shih-Hsu Huang - Chung Yuan Christian University Sheikh Ariful Islam - University of Texas Rio Grande Valley

Anand Iyer - Microsoft

Yu-Min Lee - National Yang Ming Chiao Tung University Zhixing Li - Synopsys

Rung-Bin Lin - Yuan Ze University

**Bin Lin - Cadence Design Systems**

Rajeev Murgai - Synopsys India Pvt. Ltd.

Murthy Palla - Synopsys Inc.

Chidhambaranathan Rajamanikkam - Utah State University

Andre Reis - UFRGS

**Emre Salman - Stony Brook University**

**Ioannis Savidis - Drexel University**

Jia Wang - Illinois Institute of Technology

Hua Xiang - IBM Research

Kexin Yang - Google

**Richard Yarnell - University of Central Florida**

Huan Yu - Apple

**Rui Zhang - Cadence Design Systems**

**Lining Zhang - Peking University**

#### System-level Design and Methodologies (SDM)

Bo Yuan, Rutgers University (Chair) Jeff Zhang, Arizona State University (Co-Chair)

**Committee Members:**

Mohamad Hammam Alsafrjalani - University of Miami

**Sourav Das - Intel Corporation**

**Fabiano Hessel - PUCRS**

Hana Kubatova - Czech Technical University in Prague

**Abdulrahman Mahmoud - Harvard University**

Carlos Moratelli - UFSC

Sergiu Mosanu - University of Virginia

Antonio Nunez - University of Las Palmas GC

Jan Schmidt - Czech Technical University in Prague

Jihee Seo - Synopsys

Vaibhav Verma - Qualcomm

Sai Qian Zhang - New York University

### TECHNICAL PROGRAM COMMITTEES

(continued)

#### Circuit Design, 3D Integration and Advanced Packaging (ICAP)

Abhronil Sengupta, The Pennsylvania State University (Chair) Rouwaida Kanj, Synopsys/American University of Beirut(on Leave) (Co-Chair) Harsh Patel, Rivos Inc. (Co-Chair)

#### Committee Members:

Ali Afzali-Kusha - University of Tehran Amit Agarwal - Intel Corporation Iraklis Anagnostopoulos - Southern Illinois University Carbondale Kirti Bhanushali - Cadence Design Systems Karan Bhatia - Texas Instruments, Inc. Paulo Butzen - Universidade Federal do Rio Grande Sul Yuanging Cheng - Beihang University **Tobias Gemmeke - RWTH Aachen University** Na Gong - University of South Alabama Ankur Guha Roy - Broadcom Inc. Steven Hsu - Intel Corp. Manjunath Kareppagoudr - Advanced Micro Devices inc Dae Hyun Kim - Washington State University **Rakesh Kumar - Ampere Computing** Jin-Fu Li - National Central University Rakeshkumar Mahto - California State University, Fullerton Maruthi Mukkannaiah - iota Biosciences Vojin Oklobdzija - University of California Davis **Praveen Prabha - Marvell Semiconductor** Suyash Ranjan - Qualcomm Joseph Riad - Micron Technology Thilo Sauter - Danube University Krems **Ioannis Savidis - Drexel University** Ali Shahi - GlobalFoundries Hechen Wang - Intel Labs Yanchao Wang - Broadcom zhichao Zhang - Intel Zhen Zhou - Intel Corp Amir Zjajo - Innatera Nanosystems

#### Special Sessions (SS)

Mimi Xie, The University of Texas at San Antonio (Chair) Hossein Sayadi, California State University, Long Beach (Co-Chair)

#### **WIP - Work in Progress**

Hossein Sayadi, California State University, Long Beach (Chair) Deliang Fan, Johns Hopkins University (Co-Chair) Cindy Yang Yi, Virginia Tech (Co-Chair)

### **TECHNICAL PROGRAM COMMITTEES**

(continued)

#### Hardware and System Security (HSS)

Hassan Salmani, Howard University (Chair) Ujjwal Guin, Auburn University (Co-Chair)

#### **Committee Members:**

Kanad Basu - University of Texas at Dallas Alvaro Cintas Canto - Marymount University Avani Dave - Intel Corp. Inc

Caiwen Ding - University of Connecticut Jaya Dofe - California State University

Yinghua Hu - Synopsys

Chenglu Jin - CWI Amsterdam

Jan Moritz Joseph - RWTH Aachen University

**Kyle Juretus - Villanova University**

**Everton Matos - Technology Innovation Institute**

Mehran Mozaffari Kermani - University of South Florida

Debdeep Mukhopadhyay - Department of Computer Science and Engineering, Indian Institute of Technology Kharagpur

Seetharam Narasimhan - Nvidia Corp

**Hammond Pearce - University of New South Wales**

Md Tauhidur Rahman - Florida International University

**Biswajit Ray - Colorado State University**

Francesco Regazzoni - University of Amsterdam and ALaRI - USI

Amin Rezaei - California State University, Long Beach

Soheil Salehi - Department of Electrical and Computer Engineering, University of Arizona

fareena sagib - University of North Carolina at Charlotte

**Zhijie Shi - University of Connecticut**

Dominik Sisejkovic - Corporate Research, Robert Bosch GmbH, Germany

**Benjamin Tan - University of Calgary**

Sara Tehranipoor - West Virginia University

Jiafeng Xie - Villanova University

Lian Zeng - Infineon Techologies

Jiliang Zhang - Hunan University

#### **Emerging Device and Process Technologies and Applications (EDPT)**

Rasit Onur Topaloglu, topallabs & Marist College (Chair)

Lan Wei, University of Waterloo (Co-Chair)

#### Committee Members:

Shaahin Angizi - New Jersey Institute of Technology

Ahmedullah Aziz - University of Tennessee, Knoxville

**Arijit Banerjee - Advanced Micro Devices**

Sumeet Gupta - Purdue University

Vita Pi-Ho Hu - National Taiwan University

**Huamin Li - University at Buffalo**

Chun-Yu Lin - National Yang Ming Chiao Tung University

Ankita Mohapatra - Associate Professor

Mehran Mozaffari Kermani - University of South Florida

Chenyun Pan - University of Texas at Arlington

Kun Qian - GLOBALFOUNDRIES

Ujwal Radhakrishna - Texas Instruments Inc.

Arman Roohi - University of Nebraska - Lincoln

Sonal Shreya - Aarhus University

Yanan Sun - Department of Micro-Nano Electronics, Shanghai Jiao Tong University

Jinhui Wang - University of South Alabama

Mustafa Berke Yelten - Istanbul Technical University

#### **GENERAL INFORMATION**

# GENERAL INFORMATION ISOED'24

April 3-5, 2024 Seven Hills Conference Center San Francisco State University

#### **AWARDS & RECOGNITIONS**

Wednesday April 3, 8:40 AM - 9:00 AM

Track A - Nob Hill Room

#### **Best Paper Awards**

Recipients of the ISQED'24 Best Paper Awards will be recognized in this segment of the program. The best papers are shown in Page 2 of this document.

#### Keynotes Keynote 1P.1

Wednesday, April 3, 9:00 AM - 9:35 AM

### Cross-Layer Optimization of Energy Harvesting and Storage

Naehyuck Chang

Executive Vice President, Samsung SDI America

#### Keynote 1P.2

Wednesday, April 3, 11:45 AM - 12:20 PM

# Why we did not have flying cars for 100 years

Jim Dukhovny CEO, Alef Aeronautics

#### **Panel Discussion**

Wednesday, April 3, 3:15 PM - 4:45 PM

Track A - Nob Hill Room

#### **AI Hardware: Opportunities and Challenges**

In the contemporary fabric of our civilization, artificial intelligence (AI) has emerged as a pivotal force, permeating various facets of our daily lives. Its significance lies in its ability to augment human capabilities, streamline processes, and catalyze breakthroughs in fields ranging from healthcare to finance. As Al applications become increasingly sophisticated, the importance of dedicated hardware tailored to meet the unique computational demands of these intelligent systems has come to the forefront. The growing complexity of AI algorithms, particularly in the realm of deep learning, necessitates specialized hardware architectures. Such dedicated AI hardware serves as the backbone for processing vast amounts of data and executing intricate calculations with remarkable speed and efficiency. This optimized hardware not only accelerates the training and inference processes but also contributes to the scalability and practicality of Al applications. As Al continues to evolve, researchers are uncovering novel algorithms and models that push the boundaries of what is achievable. In this dynamic landscape, the hardware supporting AI must adapt and innovate to fully realize the potential of emerging technologies. The symbiotic relationship between Al advancements and specialized hardware underscores the critical role that hardware research plays in shaping the trajectory of artificial intelligence, ensuring its seamless integration into the fabric of our technologically driven civilization. Embark on a riveting exploration of Al hardware with our expert panel. Explore the expansive potential of advanced processors and innovative accelerators, dissecting the intricate landscape that defines artificial intelligence hardware. Seasoned experts guide the audience through the dual lens of opportunities and challenges, addressing key facets such as scalability, energy efficiency, and the symbiotic interplay with software. This panel promises a compelling journey into the forefront of Al hardware, where challenges are viewed as gateways to innovation, shaping the future of computational prowess. Join us for a captivating exploration of the evolving landscape at the intersection of hardware technology and artificial intelligence.

#### **Panelists:**

#### Arnab Raha - Intel

Garrett S. Rose - University of Tennessee Knoxville Akhilesh Jaiswal - University of Wisconsin Madison Syed Shakib Sarwar - Meta Inc. Cindy Yi - Virginia Tech

#### **Modedrator & Chair:**

Ahmedullah Aziz - University of Tennessee Knoxville

### **GENERAL INFORMATION**

#### **Embedded Tutorials**

#### **Chair & Moderators:**

**Zhen Zhou -** Intel (Chair) **Hechen Wang -** Intel (Co-Chair)

#### Track A - Nob Hill Room Tutorial 1

Wednesday, April 3, 12:25 PM -1:25 PM

#### **Advanced Packaging for Heterogenous Integration**

#### Tolga Acikalin

Intel Labs

### **Tutorial 2**

Thursday April 4, 1:05 PM -2:05 PM

# Securing Ubiquitous Devices with Lightweight Circuit Primitives

#### **Prof. Kaiyuan Yang**

Rice University

#### **TECHNICAL SESSIONS**

There are a total of 20 paper sessions held on Wednesday to Friday. Technical sessions are held in the format of three parallel tracks **A**, **B**, **C** located respectively in Nob Hill Room, Russian Hill Room, and Mt. Davidson room.

#### **ON-SITE REGISTRATION**

Tentative time schedule of on-site registration is as follows:

Wednesday, April 3, 8:00 AM - 2:00 PM Thursday, April 4, 8:00 AM - 12:00 PM

Registration desk location will be at the conference center lobby.

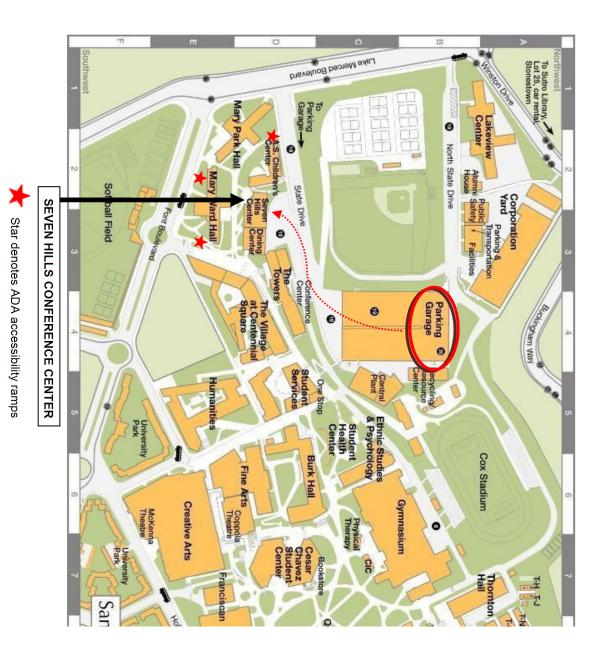

#### Seven Hills Conference Center

ISQED'24 conference will be held in Seven Hills Conference Center, located in San Francisco State University, 800 Font Blvd, San Francisco, CA 94132.

If you are using navigator the best address to use is: 796 state drive, San Francisco, CA 94132. (Note: make sure to use Google Maps app) At the end of State Drive is the Public Parking Lot ("Lot 20"). Parking is \$6.25 for less than 2 hours, and \$10 for 2+ hours. Pay stations on each floor accept \$1, \$5 and \$10 bills as well as credit/debit cards. Be advised, pay stations do not provide change. Please have exact amount. From the garage, Seven Hills' entrance can be accessed from State Drive by walking Southwest towards the A.S. Children's Center and taking the staircase beside it up one flight. Wheelchair access: go past the A.S. Children's Center and take a left onto the path. Follow to the entrance to the Seven Hills Conference Center.

8

### **UNIVERSITY MAP & CONFERENCE CENTER LOCATION+**

# **PROGRAM AT A GLANCE**

#### WEDNESDAY APRIL 3

Please note all shown times are Pacific Daylight Time (PDT)

Wednesday, April 3, 2024

|                                           |                                              |                 |                                                                               |                 | WE                                                                                                                    | DNESDA                                                                                                | AY APRIL 3                                                                              | 3               |                                                              |                                                                                                                                    |                                                         |                                             |

|-------------------------------------------|----------------------------------------------|-----------------|-------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------|

| 15:15pm-16:45pm                           |                                              | 15:10pm-15:15pm | 13:30pm-15:10pm                                                               | 13:25pm-13:30pm | 12:25pm-13:25am                                                                                                       | 11:40am-12:25pm                                                                                       | 10:20am–11:40am                                                                         | 10:10am-10:20am | 9:35am–10:10am                                               | 9:00am-9:35am                                                                                                                      | 8:40am–9:00am                                           |                                             |

| Al Hardware: Opportunities and Challenges | Panel Discussion - (Track A - Nob Hill Room) |                 | Session 2A (Nob Hill Room) Upstream Synthesis and Machine Learning            |                 | Embedded Tutorial 1 (Track A)  Advanced Packaging for Heterogenous Integration  Presenter: Tolga Acikalin, Intel Labs | ISQED Lunch Keynote Why we did not have flying cars for 100 years Jim Dukhovny, CEO, Alef Aeronautics | Session 1A (Nob Hill Room) Novel Integrated Circuits and Systems                        |                 |                                                              | Keynote:  Cross-Layer Optimization of Energy Harvesting and Storage  Naehyuck Chang, Executive Vice President, Samsung SDI America | Introduction, Committee Recognitions, Best Paper Awards | Plenary Session 1: (Track A- Nob Hill Room) |

| hallenges                                 | ob Hill Room)                                | Break           | Session 2B (Russian Hill<br>Room)<br>Hardware Trojan Attacks and<br>Detection | Break           | nous Integration                                                                                                      | s for 100 years<br>utics                                                                              | Session 1B (Russian Hill<br>Room)<br>Rapid Circuit Simulation,<br>Verification and Test | Break           | rgy Harvesting and Storage<br>President, Samsung SDI America | ergy Harvesting and Storage<br>President, Samsung SDI America                                                                      | nitions, Best Paper Awards                              | b Hill Room)                                |

|                                           |                                              |                 | Session 2C (Mt. Davidson Room)  DNN Acceleration                              |                 |                                                                                                                       |                                                                                                       | Session 1C (Mt. Davidson<br>Room)<br>Hardware Security Primitives                       |                 |                                                              |                                                                                                                                    |                                                         |                                             |

## **PROGRAM AT A GLANCE**

### **THURSDAY APRIL 4**

Thursday, April 4, 2024

Please note all shown times are Pacific Daylight Time (PDT)

|                         | 14:10nm-15:50nm                                        | 14:05pm-14:10pm | 13:05pm-14:05pm                                                                                           | 12:25pm-13:05                                     | 10:45am–12:25pm                                                                                      | 10:35am-10:45am | 9:40am-10:35am                                                        | 9:35am-9:40am | 9:00am–9:35am                                                                                                                                                                                      | 8:45am–9:00am |                                              |

|-------------------------|--------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------|

| Automation              | Session 4A (Nob Hill Room) Advances in Physical Design |                 | Securing Ubiquitous Devices with Lightweight Circuit Primitives  Presenter: Kaiyuan Yang, Rice University | Lun Embedded Tutorial 2 (Track A - Nob Hill Room) | Session 3A (Nob Hill Room) Simulation and Estimation Automation                                      |                 | Session PW1 (Nob Hill Room, Track A) Poster & WIP Session 1           |               | Keynote:  Reflections on Microelectronic and Microelectrom Implementing Emerging Technologies  Clare D. Thiem, Air Force Research Laboratory/R/TB                                                  | Welcome       | Plenary Session 2: (Track A - Nob Hill Room) |

| Side channel Signals in | Session 4B (Russian Hill<br>Room)                      | Break           | Lightweight Circuit Primitives ersity                                                                     | Lunch Break<br>Nob Hill Room)                     | Session 3B (Russian Hill<br>Room)<br>Novel Computing                                                 | Break           | Session PW2 (Russian Hill<br>Room, Track B)<br>Poster & WIP Session 2 | Break         | Keynote: Reflections on Microelectronic and Microelectromechanical Technologies and the Challenges of Implementing Emerging Technologies Clare D. Thiem, <i>Air Force Research Laboratory/RITB</i> |               | bb Hill Room)                                |

| Next Generation IoT     | Session 4C (Mt. Davidson Room)                         |                 |                                                                                                           |                                                   | Session 3C (Mt. Davidson Room) Algorithms, Architectures, and Circuits for Efficient Al/ML Computing |                 | Session PW3 (Mt. Davidson<br>Room, Track C)<br>Poster & WIP Session 3 |               | nologies and the Challenges of                                                                                                                                                                     |               |                                              |

### **FRIDAY APRIL 5**

Friday, April 5, 2024

Please note all shown times are Pacific Daylight Time (PDT)

| 10:45am–12:05pm                                                     | 10:40am-10:45am | 9:00am-10:40am                                             |  |

|---------------------------------------------------------------------|-----------------|------------------------------------------------------------|--|

| Session 6A (Nob Hill Room) FAQ: FPGAs, Accelerators, Quantum        |                 | Session 5A (Nob Hill Room) Emerging Computing Paradigms    |  |

| Session 6B (Russian Hill<br>Room)<br>Al Accelerator Hardware Design | Break           | Session 5B (Russian Hill<br>Room)<br>Learning on the Edge  |  |

| Session 6C (Mt. Davidson<br>Room)<br>Quantum Computing              |                 | Session 5C (Mt. Davidson<br>Room)<br>Al for Cyber Security |  |

### **ISQED Keynote 1P.1**

### Wednesday April 3 9:00 AM - 9:35 AM

Room: Nob Hill

### **Cross-Layer Optimization of Energy Harvesting and Storage**

Naehyuck Chang

Executive Vice President, Samsung SDI America

The use of energy harvesting is mandatory for carbon-neutral ecosystems. For portable systems, energy harvesting makes it possible to operate them without full-capacity batteries. Energy harvesting generally lacks load-following capability; harvesting-storage-use is a typical energy harvesting system structure. Appropriate power conversion processes are commonly used during the transition between harvesting, storage, and use. Material and device research is the mainstream for energy harvesting, which provides fundamental solutions for more efficient energy harvesting. However, proper system-level management is also vital. This talk will introduce several cross-layer optimization practices of the harvesting-storage-use systems for a range of applications, from wearable devices to electric vehicles and grid-connected energy storage systems. First, we will introduce the online reconfiguration of photovoltaic arrays combating partial shading with examples of stationary and onboard energy harvesting for electric vehicles. We will also mention the online reconfiguration of thermoelectric device arrays dealing with the temperature gradient of the vehicle radiator. Second, we will address radical cross-layer optimization of a wearable solar energy harvesting system, deleting the entire storage and conversion processes. We demonstrate that aggressive dynamic power management can delete the energy storage and power converters. While load following is a typical setup of the energy harvesting system, such a radical cross-layer optimization makes the load (a UV detector) follow the energy harvesting of a photovoltaic cell. Finally, we will introduce solar energy harvesting with energy storage, one of the most promising ways to overcome the Duck Curve.

#### **About Naehyuck Chang**

Naehyuck Chang is an Executive Vice President at Samsung SDI America. He was the previous Head of Development at Samsung SDI Headquarters from 2021 to 2023. Dr. Chang was in charge of all the automotive and energy-storage product developments, from cells to systems. From 1997 to 2014, he was with the Department of Computer Science and Engineering at Seoul National University. Since 2014, he has been a Full Professor at the Department of Electrical Engineering, Korea Advanced Institute of Science and Technology. Dr. Chang is a Fellow of the ACM and a Fellow of IEEE for his contributions to low-power systems. Dr. Chang is a member of the National Academy of Engineering of Korea. Dr. Chang's research interests include low-power cyber-physical systems and Design Automation of Things, such as systematic design and optimization of fuel cell systems, energy storage systems, electric vehicles, drones, and energy harvesting. Dr. Chang is specifically interested in mobility electrification in terms of design, optimization, and management of the power, energy, and lifetime of the battery cells. Dr. Chang was the Chair and the Past Chair of the ACM Special Interest Group on Design Automation. Dr. Chang was the TPC Co-Chair of DAC 2016, ASP-DAC 2015, ICCD 2014, CODES+ISSS 2012, and ISLPED 2009, and the General Co-Chair of VLSI-SoC 2015, ICCD 2015 and 2014, and ISLPED 2011. He was the recipient of the 2014 ISLPED Best Paper Award, the 2011 SAE Vincent Bendix Automotive Electronics Engineering Award, the 2011 Sinyang Academic Award, the 2009 IEEE SSCS International SoC Design Conference Seoul Chapter Award, and various ISLPED Low-Power Design Contest Awards in 2002, 2003, 2004, 2007, 2012, 2014, and 2017, respectively. Dr. Chang was the Editor-in-Chief of the ACM Transactions on Design Automation of Electronics Systems. He was an Associated Editor for the IEEE Transactions on VLSI, IEEE Transactions on CAD, ACM Transactions on Embedded Computing Systems, IEEE Embedded Systems Letters, and IEEE Transactions on Circuits and Systems Part I.

### **ISQED Keynote 1P.2**

### Wednesday April 3 11:45 AM - 12:20 PM Room: Nob Hill

### Why we did not have flying cars for 100 years

Jim Dukhovny

CEO, Alef Aeronautics

For more than a hundred years, the concept of flying cars has captured the imagination of innovators, engineers, and the general populace, promising a revolution in how we perceive personal and city travel. However, despite the long-held aspirations and technological progress, our cityscapes are yet to witness the bustling activity of airborne vehicles that many had envisioned. In his keynote speech, Jim Dukhovny, CEO of Alef Aeronautics, provides an insightful analysis into why the vision of flying cars has not materialized over the past century, dissecting the intricate array of technical, regulatory, and societal obstacles that have impeded their fruition. The presentation delves into the substantial barriers that have historically derailed this innovation. It highlights the formidable engineering feats required to produce vehicles that are both airworthy and road-ready, ensuring safety, efficiency, and reliability, alongside navigating the complex regulatory frameworks that oversee both airspace and terrestrial mobility. This exploration sheds light on the numerous elements that have maintained flying cars as a futuristic concept rather than a present-day reality.

#### **About Jim Dukhovny**

Jim Dukhovny is the CEO of Alef Aeronautics, a sustainable electric transportation company that is designing and developing the world's first flying car. Dukhovny has received education from UC Berkeley, Santa Clara University, and Stanford University. Influenced by his father, Leonid Dukhovny, a well-known singer-songwriter, poet, scientist, and avid science fiction lover, Jim Dukhovny has created a number of organizations spanning the entertainment, software, and non-profit industries. Among his notable achievements, Dukhovny cofounded and led startups such as Intellectual Casino, Transcoder, DjWizard Presents, was the president of the Science Fiction Society of Silicon Valley and contributed to the architecture of Windows 10, Walmart's online imaging system, and a number of Yahoo products. In 2015, Dukhovny, together with Constantine Kisly, Pavel Markin, and Oleg Petrov, founded Alef Aeronautics to develop the world's first flying car. The prototype of this car successfully debuted in 2022 and through pre-sales became the world's best-selling aircraft in 2023.

### **ISQED Keynote 2P.1**

Thursday April 4

9:00 AM - 9:35 AM

Room: Nob Hill

# Reflections on Microelectronic and Microelectromechanical Technologies and the Challenges of Implementing Emerging Technologies

Clare D. Thiem

Air Force Research Laboratory (AFRL)

Mr. Clare D. Thiem's keynote at ISQED'24, titled "Reflections on Microelectronic and Microelectromechanical Technologies and the Challenges of Implementing Emerging Technologies," provides a comprehensive exploration of the complex landscape surrounding the integration of emerging technologies into microelectronic and microelectromechanical systems. Leveraging extensive expertise cultivated at the Air Force Research Laboratory (AFRL), Mr. Thiem offers nuanced insights into the multifaceted challenges and opportunities inherent in this dynamic domain. By examining the intricate interplay between technological innovation and practical implementation, Thiem equips attendees with invaluable perspectives and strategies essential for navigating the ever-evolving landscape of modern engineering.

#### **About Clare D. Thiem**

Mr. Thiem is a Senior Electronics Engineer in the Air Force Research Laboratory's (AFRL's) Information Directorate's High Performance Systems Branch (RITB). His current research interests pursue the development of practical, hardware-based, biologically inspired computing technology for Department of Air Force for size, weight, and power constrained systems. He currently serves as the Air Force Program Manager for the OUSD(R&E) funded Tri-Service, A Combined Development Pipeline for Novel Neuromorphic Hardware (NeuroPipe) Tri-Service Advanced Research for the Advancement of S&T Priorities (ARAP). He is the Program Manager for the Day 1 Deployable Machine Learning Program and Chief Engineer/Deputy Program Manager for the Emerging Nanotechnology for Autonomous Systems Program. He is an AFRL/RI Topic Lead for the Extreme Neuromorphic Materials and Computing Center of Excellence (CoE), and the AFRL Lead for Computational Efficiency in the Efficient and Robust Machine Learning (ERML) CoE. Mr. Thiem leverages over 36 years of technical experience and leadership within the Department of Defense working with a variety of technologies. He earned a Master of Science, 2002, Mechanical Engineering, National Technological University, Fort Collins, CO; and a Bachelor of Science in Engineering, 1986, Aerospace Engineering, College of Engineering, The University of Michigan, Ann Arbor, Ml. He has authored/co-authored over 40 publications.

### **Panel Discussion**

# Wednesday April 3

Room: Nob Hill

### **Al Hardware: Opportunities and Challenges**

#### **Panelists:**

Arnab Raha - Intel

Garrett S. Rose - University of Tennessee Knoxville

Akhilesh Jaiswal - University of Wisconsin Madison

Syed Shakib Sarwar - Meta Inc.

Cindy Yi - Virginia Tech

#### **Modedrator/Chair:**

Ahmedullah Aziz - University of Tennessee Knoxville

#### **Summary:**

In the contemporary fabric of our civilization, artificial intelligence (AI) has emerged as a pivotal force, permeating various facets of our daily lives. Its significance lies in its ability to augment human capabilities, streamline processes, and catalyze breakthroughs in fields ranging from healthcare to finance. As Al applications become increasingly sophisticated, the importance of dedicated hardware tailored to meet the unique computational demands of these intelligent systems has come to the forefront. The growing complexity of AI algorithms, particularly in the realm of deep learning, necessitates specialized hardware architectures. Such dedicated AI hardware serves as the backbone for processing vast amounts of data and executing intricate calculations with remarkable speed and efficiency. This optimized hardware not only accelerates the training and inference processes but also contributes to the scalability and practicality of Al applications. As Al continues to evolve, researchers are uncovering novel algorithms and models that push the boundaries of what is achievable. In this dynamic landscape, the hardware supporting AI must adapt and innovate to fully realize the potential of emerging technologies. The symbiotic relationship between Al advancements and specialized hardware underscores the critical role that hardware research plays in shaping the trajectory of artificial intelligence, ensuring its seamless integration into the fabric of our technologically driven civilization. Embark on a riveting exploration of AI hardware with our expert panel. Explore the expansive potential of advanced processors and innovative accelerators, dissecting the intricate landscape that defines artificial intelligence hardware. Seasoned experts guide the audience through the dual lens of opportunities and challenges, addressing key facets such as scalability, energy efficiency, and the symbiotic interplay with software. This panel promises a compelling journey into the forefront of AI hardware, where challenges are viewed as gateways to innovation, shaping the future of computational prowess. Join us for a captivating exploration of the evolving landscape at the intersection of hardware technology and artificial intelligence.

#### **Embedded Tutorial 1**

Wednesday April 3

12:25 AM - 1:25 PM

Nob Hill Room

### **Advanced Packaging for Heterogenous Integration**

Tolga Acikalin *Intel Labs*

#### **Summary:**

Emergence of artificial intelligence and machine learning, specifically recent developments on large language models, along with trends in internet of things and big data is driving new wave of growth in semiconductors. Heterogeneous integration (HI) is a powerful and key enabler to meet the demands of continued growth of computing and communication performance. Heterogeneous integration involves the integration of separately manufactured components with different functions into a higher-level assembly that, in aggregate, provides enhanced functionality and improved operating characteristics. System level co-design and optimization will be key to achieve the best performance where packaging plays a key role. This tutorial will provide a brief evolution of packaging technologies, and focus on advanced packaging architectures for HI. Key features in 2D and 3D interconnects will be presented along with novel packaging materials (e.g. glass) as well as co-packaged optics using silicon photonics. Furthermore in this tutorial, power-delivery and thermal considerations in advanced packaging will be discussed from a system design perspective.

#### **About Tolga Acikalin**

Tolga Acikalin earned his Bachelor of Science degree in Mechanical Engineering from Middle East Technical University, Ankara, Turkey, and his Master of Science. and Ph.D. degrees from Purdue University, West Lafayette, IN. Joining Intel in 2007 as a Research and Development Engineer, he worked on various assembly and test pathfinding projects in the Technology and Manufacturing Group, Chandler, AZ. Since 2013, he has been at Intel Labs in Santa Clara, CA. He is currently a Principal Engineer with Intel Labs, driving innovative strategies for heterogeneous system integration from package to wafer scale with an emphasis on next generation interconnect technologies. His research focuses on glass for heterogeneous integration, co-packaged optics and silicon photonics, optical and sub-THz to THz RF high-speed interconnects, and their respective package architectures. Tolga has authored or co-authored more than 15 peer-reviewed conference and journal papers in leading APS, ASME, and IEEE publications and holds 5 issued patents along with over 30 filed patents.

### **Embedded Tutorial 2**

Thursday April 4

1:05 PM - 2:05 PM

Nob Hill Room

### **Securing Ubiquitous Devices with Lightweight Circuit Primitives**

**Prof. Kaiyuan Yang** *Rice University*

#### **Summary:**

Security and privacy are critical challenges to overcome for ubiquitous electronics, including IoT and wearable/implantable devices. Securing these systems faces not only new challenges at system and network levels due to a vast variance of applications, system constructions, and attack surfaces, but also severe hardware resource constraints on computation resources, power consumption, and device cost. To tackle these challenges, significant research efforts have been pursuing specialized hardware-enabled security primitives that could help build a reliable, trustful, and energy-efficient foundation for system security. This tutorial will give an overview of the problems and focus on three hardware security challenges that could be dealt with through novel circuit designs, namely entropy generation, countermeasures against side-channel and fault-injection attacks, and lightweight computing for security. I will review state-of-the-art circuit-enabled security primitives, including our recent work towards all-digital, fully synthesizable, and compact circuit techniques that enable agile SoC development and technology portability. Novel circuit principles that cross the boundary of traditional digital and analog designs have led to significant improvements in the performance and overheads of these security primitives.

#### **About Kaiyuan Yang**

Kaiyuan Yang is an Associate Professor of Electrical and Computer Engineering at Rice University, USA, where he leads the Secure and Intelligent Micro-Systems (SIMS) lab. He received his B.S. degree in Electronic Engineering from Tsinghua University, China, in 2012, and his Ph.D. degree in Electrical Engineering from the University of Michigan - Ann Arbor, in 2017. His research interests include low-power integrated circuits and system design for secure and intelligent microsystems, bioelectronics, hardware security, and mixed-signal computing. He is a recipient of the NSF CAREER Award, IEEE SSCS Predoctoral Achievement Award, Best Paper Awards at 2022 ACM MobiCom, 2021 IEEE CICC, 2016 IEEE S&P (Oakland), and 2015 IEEE ISCAS, and several best paper award nominations at premier conferences. He has given invited talks at major conferences including ISSCC, IEDM, ICCAD, RFIC, ASSCC, etc. His work was also recognized as the research highlight of Communications of ACM and ACM GetMobile magazines, the cover of Nature Biomedical Engineering, and Top Picks in Hardware and Embedded Security.

#### **SESSION 1A**

#### Wednesday April 3

#### **Novel Integrated Circuits and Systems**

Chair: Suyash Ranjan, Qualcomm, San Diego

10:20AM

1A.1

HISPE: High-Speed Configurable Floating-Point Multi-Precision Processing Element Tejas N<sup>1</sup>, Rakshit Bhatia<sup>1</sup>, Madhav Rao<sup>2</sup>

<sup>1</sup>IIIT-Bangalore, <sup>2</sup>International Institute of Information Technology-Bangalore

10:40AM

1A.2

A 0.186 pJ/bit, 6-Gb/s, Energy-Efficient, Half-Rate Hybrid Circuit Topology in 1.2V, 65 nm CMOS.

Prema Kumar Govindaswamy<sup>1</sup>, Mursina Khatun<sup>2</sup>, Vijay Shankar Pasupureddi<sup>1</sup> Indian Institute of Technology Bhubaneswar, <sup>2</sup>a23ec09005@iitbbs.ac.in

11:00AM

1A.3

A 1.2 V Double-Tail StrongARM Latch Comparator with 51 fJ/comparison and 380  $\mu$ V Input Noise in 65 nm CMOS Technology

Srinivasa Rao Maram<sup>1</sup>, Boyapati Subrahmanyam<sup>2</sup>, Vijay Shankar Pasupureddi<sup>1</sup> Indian Institute of Technology Bhubaneswar, <sup>2</sup>FH-Kaernten

11:20AM

1A.4

HiCTL: High Fan-in Differential Capacitive-Threshold-Logic Gate Implementation With An Offset-Compensated Comparator

Abdullah Sahruri<sup>1</sup>, Martin Margala<sup>1</sup>, Ugur Cilingiroglu<sup>2</sup>

<sup>1</sup>University of Louisiana at Lafayette, <sup>2</sup>Yeditepe University

#### **SESSION 1B**

#### Wednesday April 3

#### Rapid Circuit Simulation, Verification and Test

Chair: Chidhambaranathan R, Synopsys Inc.

10:20AM

1B.1

#### **Quantum Circuit Simulation with Fast Tensor Decision Diagram**

Qirui Zhang, Mehdi Saligane, Hun Seok Kim, David Blaauw, Georgios Tzimpragos, Dennis Sylvester

University of Michigan

10:40AM

1B.2

#### **Dual Use Circuitry for Early Failure Warning and Test**

Alexander Coyle<sup>1</sup>, Hui Jiang<sup>1</sup>, Jennifer Dworak<sup>1</sup>, Theodore Manikas<sup>1</sup>, Kundan Nepal<sup>2</sup>

<sup>1</sup>Southern Methodist University, <sup>2</sup>University of St Thomas

11:00AM

1B.3

#### **RTL Simulation Acceleration with Machine Learning Models**

Chandan Karfa<sup>1</sup>, Surajit Das<sup>2</sup>, Hetang Patel<sup>3</sup>, Disha Puri<sup>4</sup>, Anshul Jain<sup>4</sup>, Kartheek Bellamkonda<sup>3</sup>, Rahul Reddy<sup>3</sup>, Arijit Sur<sup>3</sup>, Pradip Prajapati<sup>5</sup>

<sup>1</sup>Indian Institute of Technology Guwahati, <sup>2</sup>Postdoctoral Research Associate, <sup>3</sup>IIT Guwahati, <sup>4</sup>Intel, <sup>5</sup>Inrtel

11:20AM

1B.4

# **Automated Assertion Checker Generator and Information Flow Tracking for Security Verification**

Miguel Alfaro Zapata, Amirhossein Shahshahani, Zeljko Zilic McGill University

#### **SESSION 1C**

#### Wednesday April 3

#### **Hardware Security Primitives**

Chair: Hossein Sayadi, California State University, Long Beach

10:20AM

1C.1

**DECOR: Enhancing Logic Locking Against Machine Learning-Based Attacks**

*Yinghua Hu*<sup>1</sup>, *Kaixin Yang*<sup>2</sup>, *Subhajit Dutta Chowdhury*<sup>2</sup>, *Pierluigi Nuzzo*<sup>2</sup> <sup>1</sup>Synopsys, <sup>2</sup>University of Southern California

10:40AM

1C.2

**TEE-Time:** A Dynamic Cache Timing Analysis Tool for Trusted Execution Environments

Quentin Forcioli, Sumanta Chaudhuri, Jean-luc Danger Telecom Paris

11:00AM

1C.3

Obfuscating Quantum Hybrid-Classical Algorithms for Security and Privacy

Suryansh Upadhyay<sup>1</sup> and Swaroop Ghosh<sup>2</sup>

<sup>1</sup>Penn State University, <sup>2</sup>Pennsylvania State University

11:20AM

1C.4

A 5T Half-SRAM Design for Cold CMOS Physical Unclonable Function Applications and Beyond

Rouwaida Kanj<sup>1</sup> and Jamil Kawa<sup>2</sup>

<sup>1</sup>Synopsys (American University of Beirut, on leave), <sup>2</sup>Synopsys

11:40AM

1C.5

Model Extraction Attack against On-device Deep Learning with Power Side Channel Jialin Liu and han wang

Jiaiin Liu ana nan wang

Temple University

### **SESSION 2A**

#### Wednesday April 3

#### **Upstream Synthesis and Machine Learning**

Chair: **Murthy Palla**, Synopsys Co-Chair: **Huan Yu**, Apple

1:30PM

2A.1

Fake Timer: An Engine for Accurate Timing Estimation in Register Transfer Level Designs

Daniela Sanchez Lopera<sup>1</sup>, Robert Kunzelmann<sup>1</sup>, Endri Kaja<sup>2</sup>, Wolfgang Ecker<sup>1</sup>

<sup>1</sup>Technical University of Munich & Infineon Technologies AG, <sup>2</sup>Technische Universität Kaiserslautern & Infineon Technologies AG

1:50PM

2A.2

#### High-Level Synthesis for Microfluidic Biochips Considering Actual Volume Management and Channel Storage

Zhengyang Chen<sup>1</sup>, Yuhan Zhu<sup>1</sup>, Zhen Chen<sup>1</sup>, Zhisheng Chen<sup>2</sup>, Genggeng Liu<sup>1</sup>

<sup>1</sup>College of Computer and Data Science, Fuzhou University, <sup>2</sup>School of Informatics, Xiamen University

2:10PM

2A.3

# **Exploration of Activation Fault Reliability in Quantized Systolic Array-Based DNN Accelerators**

Mahdi Taheri<sup>1</sup>, Natalia cherezova<sup>2</sup>, Mohammad Saeed Ansari<sup>3</sup>, Maksim Jenihhin<sup>2</sup>, ALI Mahani<sup>4</sup>, Masoud Daneshtalab<sup>5</sup>, Jaan Raik<sup>2</sup>

<sup>1</sup>PhD researcher at Tallinn university of Technology, <sup>2</sup>Tallinn University of Technology, <sup>3</sup>University of Alberta, <sup>4</sup>Shahid Bahonar University of Kerman, <sup>5</sup>KTH Royal Institute of Technology

2:30PM

2A.4

# Comparative Analysis of Graph Isomorphism and Graph Neural Networks for Analog Hierarchy Labeling

Zhengfeng Wu and Ioannis Savidis Drexel University 2:50PM

2A.5

SRAM-PG: Power Delivery Network Benchmarks from SRAM Circuits Shan Shen, Zhiqiang Liu, Wenjian Yu Tsinghua University

#### **SESSION 2B**

#### Wednesday April 3

#### **Hardware Trojan Attacks and Detection**

Chair: Mohammad Ashigur Rahman, Florida International University

1:30PM

2B.1

#### A Needle in the Haystack: Inspecting Circuit Layout to Identify Hardware Trojans

Xingyu Meng<sup>1</sup>, Abhrajit Sengupta<sup>2</sup>, Kanad Basu<sup>1</sup>

<sup>1</sup>University of Texas at Dallas, <sup>2</sup>New York University

1:50PM

2B.2

#### **Trojan Assets and Attack Vectors in Processors**

Czea Sie Chuah<sup>1</sup>, Alexander Hepp<sup>2</sup>, Christian Appold<sup>1</sup>, Tim Leinmüller<sup>1</sup>

<sup>1</sup>DENSO Automotive Deutschland GmbH, <sup>2</sup>Technical University of Munich, TUM School of Computation, Information and Technology

2:10PM

2B.3

#### **Trojan Attacks on Variational Quantum Circuits and Countermeasures**

Subrata Das and Swaroop Ghosh

The Pennsylvania State University

2:30PM

2B.4

# FAST-GO: Fast, Accurate, and Scalable Hardware Trojan Detection using Graph Convolutional Networks

Ali Imangholi<sup>1</sup>, Mona Hashemi<sup>2</sup>, Amirabbas Momeni<sup>1</sup>, Siamak Mohammadi<sup>3</sup>, Trevor E. Carlson<sup>4</sup>

<sup>1</sup>School of ECE, College of Eng., University of Tehran, <sup>2</sup>School of ECE, College of Eng., University of Tehran, and School of Computing, National University of Singapore, <sup>3</sup>School of ECE, College of Eng., University of Tehran, and School of Computing Science, IPM, <sup>4</sup>National University of Singapore

#### **SESSION 2C**

#### Wednesday April 3

#### **DNN** Acceleration

Chair: Cheng Tan, Google

1:30PM

2C.1

# Optimizing Layer-Fused Scheduling of Transformer Networks on Multi-accelerator Platforms

Steven Colleman<sup>1</sup>, Arne Symons<sup>1</sup>, Victor Jung<sup>2</sup>, Marian Verhelst<sup>1</sup> KULeuven, <sup>2</sup>ETH Zurich

1:50PM

2C.2

#### Roofline Performance Analysis of DNN Architectures on CPU and GPU Systems Prashanth H C<sup>1</sup> and Madhav Rao<sup>2</sup>

<sup>1</sup>IIIT-Bangalore, <sup>2</sup>International Institute of Information Technology-Bangalore

2:10PM

2C.3

# PSO Optimized Design of Error Balanced Weight Stationary Systolic Array Architecture for CNN

Dantu Nandini Devi<sup>1</sup>, Gandi Ajay Kumar<sup>2</sup>, Bindu G Gowda<sup>2</sup>, Madhav Rao<sup>3</sup>

<sup>1</sup>International Institute of Information Technology Bangalore, <sup>2</sup>international institute of information technology, bangalore, <sup>3</sup>International Institute of Information Technology-Bangalore

2:30PM

2C.4

# DNN Memory Footprint Reduction via Post-Training Intra-Layer Multi-Precision Ouantization

Behnam Ghavami<sup>1</sup>, Amin Kamjoo<sup>1</sup>, Lesley Shannon<sup>1</sup>, Steve Wilton<sup>2</sup>

<sup>1</sup>Simon Fraser University, <sup>2</sup>UBC

#### **SESSION PW1**

#### **Thursday April 4**

#### Poster & WIP Session 1

Chair: Cindy Yang Yi, Virginia Tech

9:40AM

PW1.1

**Error Distribution Estimation for Fixed-point Arithmetic using Program Derivatives**

Soramichi Akiyama<sup>1</sup>, Ryota Shioya<sup>2</sup>, Yuto Miyatake<sup>3</sup>, Tongxin Yang<sup>4</sup>

<sup>1</sup>Ritsumeikan University, <sup>2</sup>The University of Tokyo, <sup>3</sup>Osaka University, <sup>4</sup>Sony Semiconductor Solutions Corporation

9:45AM

PW1.2

# An Automated Exhaustive Fault Analysis Technique guided by Processor Formal Verification Methods

Endri Kaja<sup>1</sup>, Nicolas Gerlin<sup>1</sup>, Bihan Zhao<sup>1</sup>, Daniela Lopera<sup>1</sup>, Jad Halabi<sup>1</sup>, Azam Khan<sup>1</sup>, Sebastian Prebeck<sup>1</sup>, Dominik Stoffel<sup>2</sup>, Wolfgang Kunz<sup>2</sup>, Wolfgang Ecker<sup>1</sup>

<sup>1</sup>Infineon Technologies AG, <sup>2</sup>Rheinland-Pfalzische Technische Universität Kaiserslautern-Landau

9:50AM

PW1.3

### Timing-Driven High-Level Synthesis for Continuous-Flow Microfluidic Biochips

ZhengYang Ye<sup>1</sup>, Zhisheng Chen<sup>2</sup>, Youlin Pan<sup>3</sup>, Genggeng Liu<sup>3</sup>, Wenzhong Guo<sup>3</sup>, Tsung-Yi Ho<sup>4</sup>, Xing Huang<sup>5</sup>

<sup>1</sup>Fuzhou University, <sup>2</sup>Xiamen University, Xiamen, <sup>3</sup>Fuzhou University,

Fuzhou, <sup>4</sup>Department of Computer Science and Engineering, The Chinese University of Hong Kong, Hong Kong, <sup>5</sup>School of Computer Science, Northwestern Polytechnical University, Xi'an

9:55AM

PW1.4

#### Swarm - A VLSI Timing, Fanout-aware Clustering Algorithm

Christos Sotiriou<sup>1</sup>, George Goudroumanis<sup>1</sup>, Nikolaos Sketopoulos<sup>1</sup>, Christos Georgakidis<sup>2</sup>

<sup>1</sup>Univesity of Thessaly - Department of Electrical and Computer Engineering

(EECE), <sup>2</sup>University of Thessaly

10:00AM

PW1.5

# FastPASE: An AI-Driven Fast PPA Speculation Engine for RTL Design Space Optimization

Akash Levy<sup>1</sup>, Joe Walston<sup>2</sup>, Sourav Samanta<sup>2</sup>, Priyanka Raina<sup>1</sup>, Stelios Diamantidis<sup>2</sup> <sup>1</sup>Stanford University, <sup>2</sup>Synopsys, Inc.

10:05AM

PW1.6

# MORE-Router+: Multilayer Multi-capacity ORdered Escape Routing via Bus-oriented Layer Assignment

Zhenyi Gao, Sheqin Dong, Zifei Cheng, Wenjian Yu Tsinghua University

10:10AM

PW1.7

# **EDA-ML:** Graph Representation Learning Framework for Digital IC Design Automation

Pratik Shrestha and Ioannis Savidis Drexel University

10:15AM

PW1.8

### **Graph Neural Network-Based Detailed Placement Optimization Framework**

DhoUI Lim<sup>1</sup> and Heechun Park<sup>2</sup>

<sup>1</sup>Kookmin University, School of Electrical Engineering, <sup>2</sup>UNIST

10:20AM

PW1.9

#### Ultra-Low Voltage Enablement for Standard Cells with Moment based LVF

ROHIT GUPTA, Chiranjeev Grover, Etienne Maurin, Olivier Minez, Jean-arnaud Francois. Sebastien Marchal

**STMicroelectronics**

10:25AM

PW1.10

# Advancing Analog Reservoir Computing through Temporal Attention and MLP Integration

Khalil Sedki and Yang Yi

Virginia Tech

#### SESSION PW2

#### **Thursday April 4**

#### Poster & WIP Session 2

Chair: Hossein Sayadi, California State University, Long Beach

9:40AM

PW2.1

Unleashing Energy-Efficiency: Neural Architecture Search without Training for Spiking Neural Networks on Loihi Chip

Shiya Liu and Yang Yi Virginia Tech

9:45AM

PW2.2

**Composite Sub-surface Model for RF GaN-HEMTs**

Xing Zhou<sup>1</sup>, Wanlan Yang<sup>1</sup>, Siau Ben Chiah<sup>2</sup>

<sup>1</sup>Nanyang Technological University, <sup>2</sup>New Silicon Corporation Pte Ltd

9:50AM

PW2.3

RASH: Reliable Deep Learning Acceleration using Sparsity-based Hardware

Shamik Kundu<sup>1</sup>, ARNAB RAHA<sup>2</sup>, Deepak Mathaikutty<sup>2</sup>, Kanad Basu<sup>1</sup>

<sup>1</sup>University of Texas at Dallas, <sup>2</sup>Intel Corporation

9:55AM

PW2.4

**Exploring Model Poisoning Attack to Convolutional Neural Network Based Brain Tumor Detection Systems**

Kusum Lata<sup>1</sup>, Prashant Singh<sup>2</sup>, Sandeep Saini<sup>2</sup>

<sup>1</sup>LNMIIT Jaipur, <sup>2</sup>The LNM Institute of Information Technology, Jaipur

10:00AM

PW2.5

Sensitivity Analysis of SOT-MTJs to Manufacturing Process Variation: A Hardware Security Perspective

Mousam Hossain<sup>1</sup>, Muhtasim Alam Chowdhury<sup>2</sup>, Ronald DeMara<sup>1</sup>, Soheil Salehi<sup>3</sup>

<sup>1</sup>University of Central Florida, <sup>2</sup>University of Arizona, <sup>3</sup>Department of Electrical and Computer Engineering, University of Arizona

10:05AM

PW2.6

#### Lightweight Multicast Authentication in NoC-based SoCs

Hansika Weersena and Prabhat Mishra University of Florida

10:15AM

PW2.7

# Trimming The Fat: A Minimum-Security Architecture for Protecting SoC Designs Against Supply Chain Threats

Kshitij Raj<sup>1</sup>, Aritra Bhattacharyay<sup>2</sup>, Swarup Bhunia<sup>3</sup>, Sandip Ray<sup>4</sup>

<sup>1</sup>University of Florida, <sup>2</sup>Department of Electrical and Computer Engineering, University of Florida, <sup>3</sup>Department of Electrical and Computer Engineering, University of Florida, <sup>4</sup>Department of Electrical and Computer Engineering, University of Florida, Gainesville

10:20AM

**PW2.8**

# Blending Scheduling Barriers: A Hybrid Approach for FPGA-based Post-Quantum Cryptography

Capucine Berger-Sigrist<sup>1</sup> and Andrea Guerrieri<sup>2</sup> <sup>1</sup>EPFL, <sup>2</sup>EPFL and HES-SO

10:25AM

PW2.9

# A Low-cost keyword spotting architecture based on wavelet packets feature extraction for edge devices

Sayed Salehi and Prakash Dhungana University of Kentucky

#### **SESSION PW3**

#### **Thursday April 4**

#### Poster & WIP Session 3

Chair: **Deliang Fan**, Johns Hopkins University

9:40AM

PW3.1

SCORCH: Neural Architecture Search and Hardware Accelerator Co-design with Reinforcement Learning

Siqin Liu and Avinash Karanth Ohio University

9:45AM

PW3.2

SpotLight: A Hotspot-Greedy, Light-Weighted, and Automated Thermal Modeling Framework for Early Smartphone Design

Chin-Wei Wu<sup>1</sup>, Yu-Min Lee<sup>2</sup>, Pei-Yu Huang<sup>2</sup>, Bo-Jiun Yang<sup>1</sup>, Tai-Yu Chen<sup>1</sup>, Ting-Chang Huang<sup>1</sup>, Yen-Lin Lee<sup>1</sup>

<sup>1</sup>MediaTek Inc., <sup>2</sup>National Yang Ming Chiao Tung University

9:50AM

PW3.3

Performance-Aware Design of Approximate Integrated MAC Factored Systolic Array Accelerators

Dantu Nandini Devi<sup>1</sup>, Gandi Ajay Kumar<sup>2</sup>, Bindu G Gowda<sup>2</sup>, Madhav Rao<sup>3</sup>

<sup>1</sup>International Institute of Information Technology Bangalore, <sup>2</sup>international institute of information technology, bangalore, <sup>3</sup>International Institute of Information Technology-Bangalore

9:55AM

PW3.4

An Energy-Efficient time Domain Based Compute In-Memory Architecture for Binary Neural Network

Subhradip Chakraborty<sup>1</sup>, Dinesh Kushwaha<sup>2</sup>, Abhishek Goel<sup>3</sup>, Anmol Singla<sup>4</sup>, Anand Bulusu<sup>3</sup>, Sudeb Dasgupta<sup>3</sup>

<sup>1</sup>RGIPT Uttar Pradesh, <sup>2</sup>Student, <sup>3</sup>IIT Roorkee, <sup>4</sup>NIT Uttarakhand

10:00AM

PW3.5

#### A multi band flexible N-path filter suited for non-contiguous channel aggregation

Chadi Jabbour

Telecom Paris

10:05AM

PW3.6

#### Hardware Trojans in Quantum Circuits, Their Impacts, and Defense

Rupshali Roy<sup>1</sup>, Subrata Das<sup>2</sup>, Swaroop Ghosh<sup>1</sup>

<sup>1</sup>Pennsylvania State University, <sup>2</sup>The Pennsylvania State University

10:10AM

PW3.7

# Thinking Outside the Clock: Physical Design for Field-coupled Nanocomputing with Deep Reinforcement Learning

Simon Hofmann, Marcel Walter, Lorenzo Servadei, Robert Wille Technical University of Munich

10:15AM

PW3.8

#### Non-parametric Greedy Optimization of Parametric Quantum Circuits

Koustubh Phalak and Swaroop Ghosh

Pennsylvania State University

10:20AM

PW3.9

#### Merits of Time-Domain Computing for VMM - A Quantitative Comparison

Florian Freye<sup>1</sup>, Jie Lou<sup>1</sup>, Christian Lanius<sup>1</sup>, Tobias Gemmeke<sup>2</sup>

<sup>1</sup>Chair of Integrated Digital Systems and Circuit Design at RWTH Aachen University, <sup>2</sup>RWTH Aachen University

10:25AM

PW3.10

#### nvXNOR Design with Enhanced Store Capability for BNN Applications

Zeinab Soueidan<sup>1</sup> and Rouwaida Kanj<sup>2</sup>

<sup>1</sup>American University of Beirut, <sup>2</sup>Synopsys, American University of Beirut on Leave

#### **SESSION 3A**

#### **Thursday April 4**

#### **Simulation and Estimation Automation**

Chair: Chidhambaranathan Rajamanikkam, Synopsys

Co-Chair: Zhong Guan, UC Santa Barbara

10:45AM

3A.1

**Fast Current Constraints Generation for Chip Safety**

Cedric Feghali and Farid Najm

University of Toronto

11:05AM

3A.2

**Toward Early Stage Dynamic Power Estimation: Exploring Alternative Machine Learning Methods and Simulation Schemes**

Philipp Fengler<sup>1</sup>, Sani Nassif<sup>2</sup>, Ulf Schlichtmann<sup>1</sup>

<sup>1</sup>Technical University of Munich, <sup>2</sup>Technical University of Munich & Radyalis

11:25AM

3A.3

A novel virtual prototyping methodology for timing-accurate simulation of AMS circuits

Teo Vallone<sup>1</sup>, Hayri Hasou<sup>2</sup>, Ernesto Colizzi<sup>2</sup>, Sara Vinco<sup>3</sup>, Davide Zoni<sup>1</sup>

<sup>1</sup>Politecnico di Milano, <sup>2</sup>Infineon Technologies, <sup>3</sup>Politecnico di Torino

11:45AM

3A.4

GridVAE: Fast Power Grid EM-Aware IR Drop Prediction and Fixing Accelerated by Variational AutoEncoder

Yibo Liu and Sheldon Tan

University of Califronia, Riverside

12:05PM

3A.5

Full Stage Delay Calculation Using Full Waveform Propagation and Standard Library CCS Model

Stavros Simoglou<sup>1</sup>, Iordanis Lilitsis<sup>2</sup>, Nikolaos Blias<sup>2</sup>, Christos Sotiriou<sup>2</sup>

<sup>1</sup>Synopsys, <sup>2</sup>Univesity of Thessaly - Department of Electrical and Computer Engineering (EECE)

#### **SESSION 3B**

#### **Thursday April 4**

#### **Novel Computing**

Chair: Kang Jun Bai, Air Force Research Laboratory

10:45AM

3B.1

**An FPGA-based Max-K-Cut Accelerator Exploiting Oscillator Synchronization Model** *Mohammad Khairul Bashar*<sup>1</sup>, *Zheyu Li*<sup>2</sup>, *Vijaykrishnan Narayanan*<sup>2</sup>, *Nikhil Shukla*<sup>1</sup> University of Virginia, <sup>2</sup>Pennsylvania State University

11:05AM

3B.2

A Comparative Analysis of Microrings Based Incoherent Photonic GEMM Accelerators Sairam Sri Vatsavai, Venkata Sai Praneeth Karempudi, Oluwaseun Alo, Ishan Thakkar University of Kentucky

11:25AM

3B.3

A SIMD Dynamic Fixed Point Processing Engine for DNN Accelerators

Gopal Raut<sup>1</sup>, PRANOSE EDAVOOR<sup>2</sup>, DAVID SELVAKUMAR<sup>3</sup>, ritambhara thakur<sup>1</sup> <sup>1</sup>CDAC Bangalore, <sup>2</sup>CENTRE FOR DEVELOPMENT OF ADVANCED COMPUTING, <sup>3</sup>C-DAC, BANGALORE

11:45AM

3B.4

**Exploring Hardware Activation Function Design: CORDIC Architecture in Diverse Floating Formats**

Mahati Basavaraju<sup>1</sup>, Vinay R<sup>1</sup>, Madhav Rao<sup>2</sup>

<sup>1</sup>International Institute of Information Technology, Bangalore, <sup>2</sup>International Institute of Information Technology-Bangalore

#### **SESSION 3C**

#### **Thursday April 4**

### Algorithms, Architectures, and Circuits for Efficient AI/ML Computing

Chair: Wen Zhang, Wright State University

10:45AM

3C.1

# **Single-Ferroelectric FET based Associative Memory for Data-Intensive Pattern Matching**

Jiayi Wang, Songyu Sun, Xunzhao Yin Zhejiang University

11:05AM

3C.2

# sLLM: Accelerating LLM Inference using Semantic Load Balancing with Shared Memory Data Structures

Jieyu Lin<sup>1</sup>, Sai Qian Zhang<sup>2</sup>, Alberto Leon-Garcia<sup>1</sup> University of Toronto, <sup>2</sup>New York University

11:25AM

3C.3

# Hyperdimensional Computing vs. Neural Networks: Comparing Architecture and Learning Process

Dongning Ma<sup>1</sup>, Cong Hao<sup>2</sup>, Xun Jiao<sup>1</sup>

<sup>1</sup>Villanova University, <sup>2</sup>Georgia Institute of Technology

11:45AM

3C.4

#### **Fused Functional Units for Area-Efficient CGRAs**

Ron Jokai, Cheng Tan, Jeff Zhang ASU

12:05PM

3C.5

#### Hardware Support for Trustworthy Machine Learning: A Survey

Md Shohidul Islam<sup>1</sup>, Ihsen Alouani<sup>2</sup>, Khaled N. Khasawneh<sup>1</sup>

<sup>1</sup>George Mason University, <sup>2</sup>CSIT, Queen's University Belfast, UK

## **SESSION 4A**

### **Thursday April 4**

## **Advances in Physical Design Automation**

Chair: Zhong Guan, UC Santa Barbara

Co-Chair: Ioannis Savidis, Drexel University

2:10PM

4A.1

Design-Technology Co-Optimization with Standard Cell Layout Generator for Pin Configurations

Junghyun Yoon<sup>1</sup> and Heechun Park<sup>2</sup>

<sup>1</sup>Kookmin University, School of Electrical Engineering, <sup>2</sup>UNIST

2:30PM

4A.2

Routing Intent Aware Pin Access Point Selection for Standard Cell Designs

Po-Chun Wang, Kai-Jie Ton, Rung-Bin Lin

Yuan Ze University

2:50PM

4A.3

SLO-ECO: Single-Line-Open Aware ECO Detailed Placement and Detailed Routing Co-Optimization

Joong-Won Jeon<sup>1</sup>, Andrew Kahng<sup>2</sup>, Jae-Hyun Kang<sup>1</sup>, Jaehwan Kim<sup>1</sup>, Mingyu Woo<sup>2</sup>

<sup>1</sup>Samsung Foundry, <sup>2</sup>UCSD

3:10PM

4A.4

Parasitic Capacitance Patterns Grid Density Binarization and Shifted Reflection Step Sequence Encoding for Dimensionality Reduction

Ping Li and Zhong Guan Sun Yat-sen University

## **SESSION 4B**

### **Thursday April 4**

## Side channel Signals in Hardwrare Security

Chair: Ujjwal Guin, Auburn University

2:10PM

4B.1

## Side-channel-driven Intrusion Detection System for Mission Critical Unmanned Aerial Vehicles

Alejandro Almeida, Muneeba Asif, Md Tauhidur Rahman, Mohammad Rahman Florida International University

2:30PM

4B.2

#### Deep Learning Enhanced Side Chanel Analysis on CRYSTALS-Kyber

Tuan Hoang, Mark Kennaway, Dung Pham, Son Mai, Ayesha Khalid, Ciara Rafferty, Maire O'Neill

Queen's University Belfast

2:50PM

4B.3

### Thermo-Attack Resiliency: Addressing a New Vulnerability in Opto-Electrical Networkon-Chips

Mahdi Hasanzadeh<sup>1</sup>, Meisam Abdollahi<sup>2</sup>, Amirali Baniasadi<sup>2</sup>, Ahmad Patooghy<sup>3</sup>

<sup>1</sup>North Carolina A & T State University, <sup>2</sup>University of Victoria, <sup>3</sup>North Carolina A&T State University

3:10PM

4B.4

#### **Enhanced Detection of Thermal Covert Channel Attacks in Multicore Processors**

Krithika Dhananjay<sup>1</sup>, Vasilis Pavlidis<sup>2</sup>, Ayse Coskun<sup>3</sup>, Emre Salman<sup>1</sup> Stony Brook University, <sup>2</sup>University of Manchester, <sup>3</sup>Boston University

3:30PM

4B.5

## RTL Interconnect Obfuscation By Polymorphic Switch Boxes For Secure Hardware Generation

Haimanti Chakraborty and Ranga Vemuri University of Cincinnati

## **SESSION 4C**

## **Thursday April 4**

#### **Next Generation IoT**

Chair: **Jeff (Jun) Zhang**, Arizona State University

2:10PM

4C.1

Enhancing Self-sustaining IoT Systems with Autonomous and Smart UAV Data Ferry Mason Conkel<sup>1</sup>, Wen Zhang<sup>2</sup>, Chen Pan<sup>3</sup>

<sup>1</sup>The University of Texas at San Antonio (UTSA), <sup>2</sup>Wright State University, <sup>3</sup>The University of Texas at San Antonio

2:30PM

4C.2

**Learning Client Selection Strategy for Federated Learning across Heterogeneous Mobile Devices**

Sai Qian Zhang<sup>1</sup>, Jieyu Lin<sup>2</sup>, Qi Zhang<sup>3</sup>, Yu-Jia Chen<sup>4</sup>

<sup>1</sup>New York University, <sup>2</sup>University of Toronto, <sup>3</sup>Microsoft, <sup>4</sup>National Central University

2:50PM

4C.3

Deep Learning Based IoT System for Real-time Traffic Risk Notification

Sahidul Islam<sup>1</sup>, Seth Klupka<sup>2</sup>, Ramin Mohammadi<sup>2</sup>, Yufang Jin<sup>3</sup>, Mimi Xie<sup>1</sup>

<sup>1</sup>The University of Texas at San Antonio, <sup>2</sup>UTSA, <sup>3</sup>University of Texas at San Antonio

3:10PM

4C.4

**Learning-Based Secure Spectrum Sharing for Intelligent IoT Networks**

Amir Alipour-Fanid<sup>1</sup>, Monireh Dabaghchian<sup>2</sup>, Long Jiao<sup>3</sup>, Kai Zeng<sup>4</sup>

<sup>1</sup>University of the District of Columbia, <sup>2</sup>Morgan State University, <sup>3</sup>University of Massachusetts Dartmouth, <sup>4</sup>George Mason University

## **SESSION 5A**

### Friday April 5

## **Emerging Computing Paradigms**

Chair: Ahmedullah Aziz, The University of Tennessee, Knoxville

9:00AM

5A.1

## Design and Evaluation of Parametric NTT Hardware Unit using different Multiplier based Modular Reduction Techniques

Lokesh Maji<sup>1</sup>, Aman Prajapati<sup>1</sup>, Madhav Rao<sup>2</sup>

<sup>1</sup>International Institute of Information Technology Bangalore, <sup>2</sup>International Institute of Information Technology-Bangalore

9:20AM

5A.2

## Multi-ALM: Run-time Multi-Level Reconfigurable Approximate Logarithmic Multiplier

Maliha Tasnim, Chinmay Raje, Sheldon Tan University of California Riverside

9:40AM

5A.3

# SRAM-Based Analog Compute-In-Memory Architecture Using C-2C Ladder And Signal Margin Assisted Design Methodology

Dinesh Kushwaha<sup>1</sup>, Ashish Joshi<sup>2</sup>, Abhishek Goel<sup>3</sup>, Rajiv Joshi<sup>4</sup>, Sudeb Dasgupta<sup>3</sup>, Anand Bulusu<sup>3</sup>

<sup>1</sup>Student, <sup>2</sup>Intel India, <sup>3</sup>IIT Roorkee, <sup>4</sup>IBM TJ Watson

10:00AM

5A.4

# Efficient Radix-4 Approximated Modified Booth Multiplier for Signal Processing and Computer Vision: A Probabilistic Design Approach

Bindu G Gowda<sup>1</sup>, Prashanth H C<sup>2</sup>, Muralidhara V N<sup>3</sup>, Madhav Rao<sup>3</sup>

<sup>1</sup>International Institute of Information Technology, Bangalore, <sup>2</sup>IIIT-Bangalore, <sup>3</sup>International Institute of Information Technology-Bangalore

## 10:20AM

5A.5

# Reprogrammable Time-Domain RRAM Based Vector Matrix Multiplier for In-Memory Computing

Bipul Boro, Rushik Parmar, Ashvinikumar Dongre, Gaurav Trivedi Indian Institute of Technology Guwahati

## **SESSION 5B**

### Friday April 5

## Learning on the Edge

Chair: **Jeff (Jun) Zhang**, Arizona State University

9:00AM

5B.1

## **AutoAnnotate: Reinforcement Learning based Code Annotation for High Level Synthesis**

Hafsah Shahzad<sup>1</sup>, Ahmed Sanaullah<sup>2</sup>, Sanjay Arora<sup>2</sup>, Ulrich Drepper<sup>2</sup>, Martin Herbordt<sup>1</sup> Boston University, <sup>2</sup>RedHat Inc.

9:20AM

5B.2

#### Write Intensity based Foresightful Page Migration for Hybrid memories

Aswathy NS<sup>1</sup> and Hemangee Kapoor<sup>2</sup>

<sup>1</sup>IIT Guwahati, <sup>2</sup>Indian Institute of Technology Guwahati

9:40AM

5B.3

# RTKWS: Real-Time Keyword Spotting Based on Integer Arithmetic for Edge Deployment

Prakash Dhungana and Sayed Salehi

University of Kentucky

10:00AM

5B.4

## Bring it On: Kinetic Energy Harvesting to Spark Machine Learning Computations in IoTs

sanket shukla and Sai Manoj Pudukotai Dinakarrao

George mason university

10:20AM

5B.5

# Code-Based Cryptography for Confidential Inference on FPGAs: An End-to-End Methodology

Rupesh Karn<sup>1</sup>, Johann Knechtel<sup>2</sup>, Ozgur Sinanoglu<sup>2</sup>

<sup>1</sup>New York University, <sup>2</sup>New York University Abu Dhabi

## **SESSION 5C**

### Friday April 5

### **AI for Cybersecurity**

Chair: Hossein Sayadi, California State University, Long Beach

9:00AM

5C.1

#### LLM-FIN: Large Language Models Fingerprinting Attack on Edge Devices

Najmeh Nazari<sup>1</sup>, Furi Xiang<sup>1</sup>, Chongzhou Fang<sup>2</sup>, Hosein Mohammadi Makrani<sup>2</sup>, Aditya Puri<sup>1</sup>, Kartik Patwari<sup>1</sup>, Hossein Sayadi<sup>3</sup>, Setareh Rafatirad<sup>4</sup>, Chen-Nee Chuah<sup>1</sup>, Houman Homayoun<sup>4</sup>

<sup>1</sup>UC Davis, <sup>2</sup>University of California, Davis, <sup>3</sup>California State University, Long Beach, <sup>4</sup>University of California Davis

9:20AM

5C.2

## Always be Pre-Training: Representation Learning for Network Intrusion Detection with GNNs

Zhengyao Gu<sup>1</sup>, Diego Lopez<sup>1</sup>, Lilas Alrahis<sup>2</sup>, Ozgur Sinanoglu<sup>2</sup> <sup>1</sup>New York University, <sup>2</sup>New York University Abu Dhabi

9:40AM

5C.3

## NAND Flash-Based Digital Fingerprinting for Robust and Secure Hardware Authentication

Kamrul Hasan<sup>1</sup>, Sara Tehranipoor<sup>1</sup>, Nima Karimian<sup>1</sup>, Surbhi Vasudeva<sup>2</sup>

<sup>1</sup>West Virginia University, <sup>2</sup>San Jose State University

10:00AM

5C.4

# Intelligent Malware Detection based on Hardware Performance Counters: A Comprehensive Survey

Hossein Sayadi<sup>1</sup>, Zhangying He<sup>1</sup>, Hosein Mohammadi Makrani<sup>2</sup>, Houman Homayoun<sup>3</sup> <sup>1</sup>California State University, Long Beach, <sup>2</sup>University of California, Davis, <sup>3</sup>University of California Davis

## **SESSION 6A**

### Friday April 5

### FAQ: FPGAs, Accelerators, Quantum

Chair: Rasit Topaloglu, topallabs & Marist College